IEEE 802.3cg® 10BASE-T1S Analog Front-End

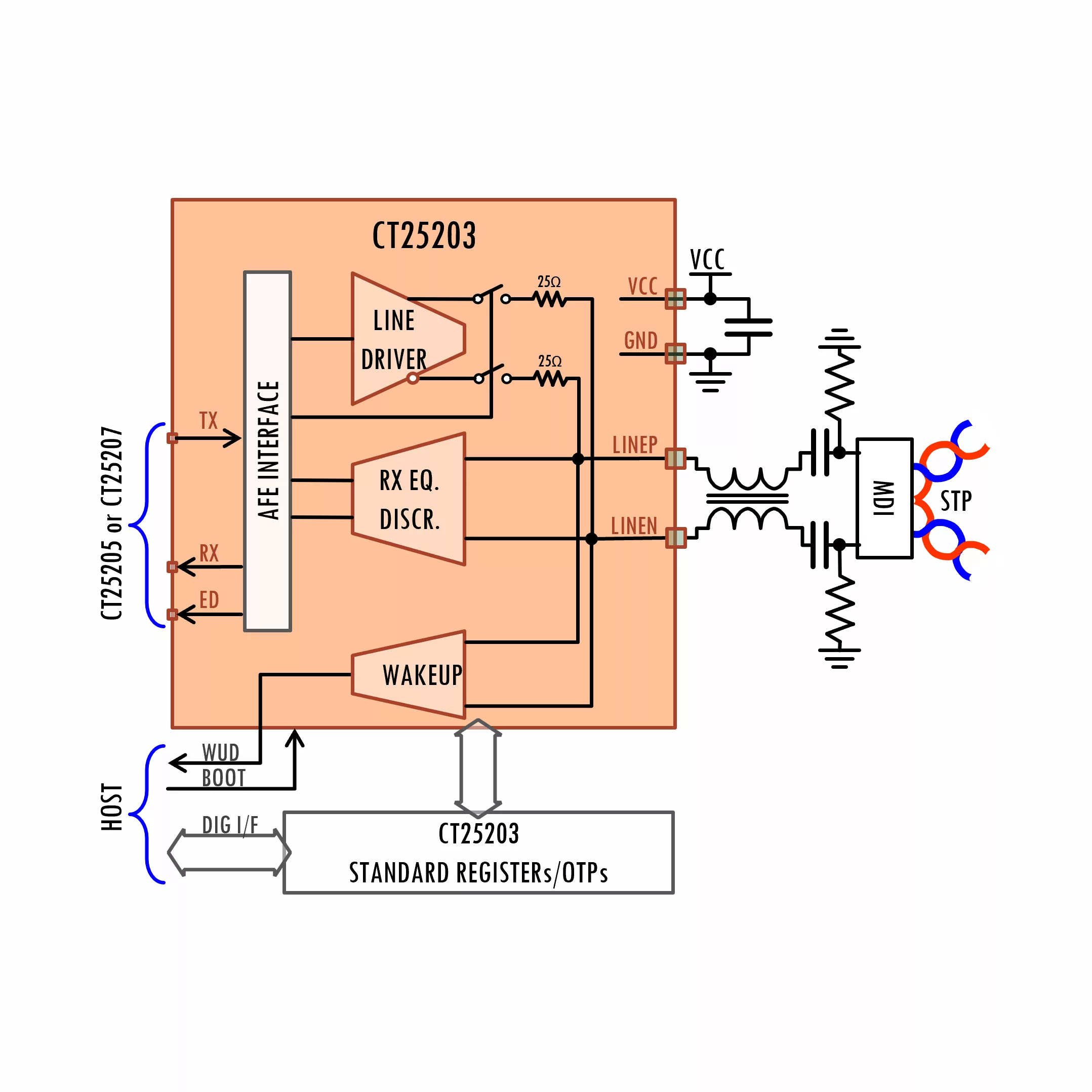

The CT25203 implements the analog front end of an IEEE 802.3cg® 10BASE-T1S physical layer.

Overview

The CT25203 implements the analog front end of an IEEE 802.3cg® 10BASE-T1S physical layer.

It can be used in conjunction to other analog and digital blocks like (a) the CT25205 to implement a complete physical layer ethernet device, (b) the CT25207 to implement a complete OPEN Alliance PMD Interface and (c) the CT25209, the CT25208 and the CT25205 to implement a complete OPEN Alliance MACPHY.

The CT25203 has been designed in GlobalFoundries 130n-BCD process but also successfully and timely ported in other BCD silicon process technologies.

Availability of a complete IEEE physical layer Test Chip vehicle (CT25205_TC) and Evaluation Boards.

The BCD process is required to meet all EMI directives to be used in the Automotive and Industrial environments.

Key features

- Compliant to:

- IEEE 802.3cg® specifications

- OPEN Alliance TC14 Interoperability Specifications

- OPEN Alliance TC14 EMC Specifications

- OPEN Alliance TC14 System Implementation

- One-fits-all Analog Macro for implementing:

- IEEE 802.3cg® 10BASE-T1S Physical Layer

- OPEN Alliance TC6 10BASE-T1S MACPHY

- OPEN Alliance TC14 10BASE-T1S PMD I/F

- Single min 3.3V supply

- Low Power consumption meeting OPEN Alliance TC10 requirement in sleep mode

- OPEN Alliance TC10 Wake Up detection

- Voltage and current references, test infrastructures, included

- Supply regulators, 25MHz XTAL and x4 (100MHz) DLL available upon request in the target silicon process.

Block Diagram

Applications

- Automotive Networks

- Industrial Networks

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Analog Front End IP core

Modeling and Verification of Mixed Signal IP using SystemVerilog in Virtuoso and NCsim

Is there a "one-size fits all" SOC PLL?

Enhance circuit timing design with programmable clock generators (Part 1 of 2)

Standard CMOS Ultrawideband Single-Chip Solutions

Comms rides power lines via optical AFE

Frequently asked questions about Analog Front End IP cores

What is IEEE 802.3cg® 10BASE-T1S Analog Front-End?

IEEE 802.3cg® 10BASE-T1S Analog Front-End is a Analog Front End IP core from Canova Tech Srl listed on Semi IP Hub.

How should engineers evaluate this Analog Front End?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Analog Front End IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.