Overview

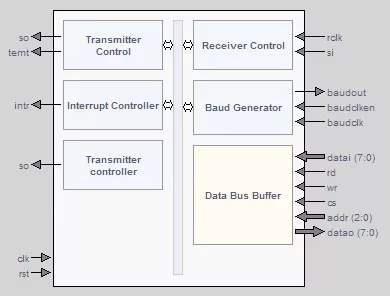

The D2698 is a Octal UART Core software compatible with the SC2698. The core contains: 3 character receiver FIFO, extended baud rate, programmable receiver and transmitter interrupts. The D2698 Octal Universal Asynchronous Receiver/Transmitter (DUART) is a communications device that provides two full-duplex asynchronous receiver/transmitter channels in a single package. It interfaces directly with microprocessors and may be used in a polled or interrupt driven systems and provides modem interface. The operating mode and data format of each channel can be programmed independently. Additionally, each receiver and transmitter can select its operating speed as one of 26 fixed baud rates, a 16X clock derived from a programmable counter/timer, or an external 1X or 16X clock. The baud rate generator and counter/timer can operate directly from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the UART particularly attractive for dual-speed channel applications such as clustered terminal systems.

Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about UART IP core

With the increasing number of high-profile data and privacy breaches in the Internet of Things (IoT) systems, businesses and consumers have a greater awareness of the need for security when buying connected products.

The universal asynchronous receiver/transmitter (UART) is an old friend to embedded systems engineers. It's probably the first communications protocol that we learn in college. In this article, we will design our very own UART using MyHDL.

Post-quantum cryptography (PQC) is moving from theory to engineering reality. With NIST-standardized algorithms ML-KEM (FIPS 203) and ML-DSA (FIPS 204) now finalized, FPGA developers face a practical challenge: How to integrate these algorithms efficiently on resource-constrained hardware?

In today’s connected world, where data is a crucial asset in SoCs, Part V of our series explores how to protect and encrypt data, whether at rest, in transit, or in use building on our earlier blog posts of the series: Essential security features for digital designers, key management, secure boot, and runtime integrity.

Most foundries provide GPIO libraries to their fabless customers. These libraries contain different elements like supply/ground pads, analog I/Os, digital I/Os, corner cells, filler cells, power-on-reset circuits. Frequently the foundry includes cells for different voltage domains. In 40nm CMOS the IC designer can use cells for 1.8V, 2.5V and 3.3V for instance.

Build safety-critical automotive, aeronautic, space and other systems with the Functional Safety RISC-V Processor IP core from CAST and PolarFire® FPGAs.