UART Serial Interface Controller

The UART_CONT IP Core is a robust UART-compliant serial interface controller capable of receiving and transmitting bits serially.

Overview

The UART_CONT IP Core is a robust UART-compliant serial interface controller capable of receiving and transmitting bits serially. It has a configurable data payload from 5 to 8-bits (with or without parity) and supports either 1 or 2 stop bits.

Both the receiver and transmitter circuits have a configurable FIFO which may be used to buffer the parallel input and output data as required. In addition, the controller features a number of flags and counters to indicate the state of the FIFOs and also whether a data word has been received or sent.

In the standard configuration, the controller will support baud rates from 2400 to 921600 baud, although higher and lower rates may be supported depending on the choice of system clock frequency. Fully custom baud rates may also be implemented on request.

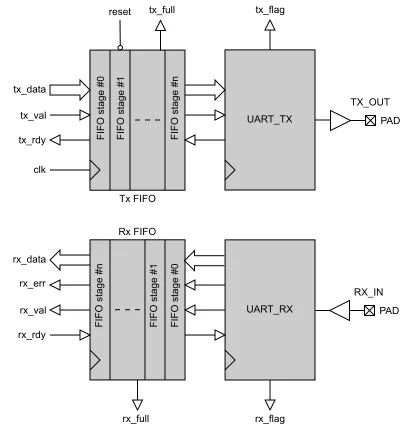

The UART controller is comprised of four main blocks as described by Figure 1. These blocks are the receiver (de-serializer), the transmitter (serializer) and the receive and transmit FIFOs.

Both the receive and transmit FIFOs use a simple data streaming protocol with a valid/ready handshake. Data is written or read from the FIFOs on the rising-edge of clk when val and rdy are both high.

The transmit FIFO may be used to 'queue up' a sequence of bytes to be sent via the UART interface. Likewise, the receive FIFO may be used to buffer incoming bytes. When the receive FIFO is full the flag rx_full is asserted and will remain high until the FIFO is emptied. If the receive FIFO is full, then any further bytes received will be lost until the FIFO has sufficient capacity.

Both the transmit and receive FIFOs have an external counter signal called tx_count and rx_count. These counter values are updated on every clock cycle and indicate the number of occupied entries in the respective FIFOs. The counter values may be used to determine how full or empty the FIFOs are at any time.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human-readable VHDL source code. (Verilog translation may be provided on request).

- UART compatible serial interface controller

- Receive and transmit input/output FIFOs with configurable depth

- Supports all standard data rates from 9600 to 921600 baud

- Fully custom data rates also supported - limited only by system clock frequency

- 5, 6, 7 or 8-bit data payload width with 1 or 2 stop bits

- Even, odd, mark, space or no parity

- Receive and transmit interrupt flags

- Rx and Tx FIFO count values and full flags

Block Diagram

Applications

- UART communications using a range of electrical standards such as RS232, RS422 and RS485 etc.

- Control in industrial, commercial and lab environments

- Basic PC-to-board interfacing and debug – including simple comms using a range of popular USB-to-UART bridge ICs

- Ideal for micro-controller communications between FPGA and MCU

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is UART Serial Interface Controller?

UART Serial Interface Controller is a UART IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.