Frac-N PLL on Samsung 4nm LN04LPP

PLLF0434X is a 1.2V/0.75V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

Overview

PLLF0434X is a 1.2V/0.75V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

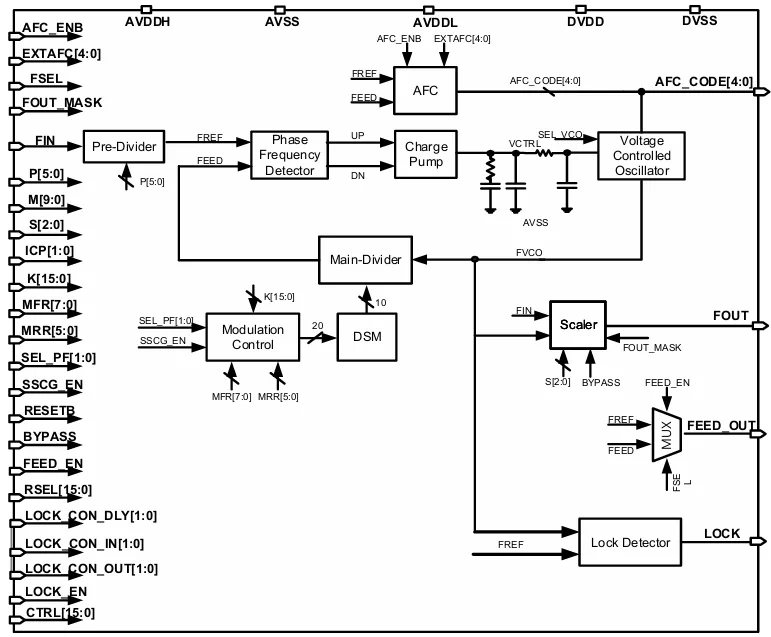

It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre-divider, a 10-bit main-divider, a 3-bit scaler, a delta-sigma modulator (DSM) and an automatic frequency control (AFC).

The maximum output frequency of PLL is 4.5GHz.

Key features

- Dual power supply of 1.2V±10% and 0.85V+5% ~ 0.75V-10%

- Operating junction temperature(TJ): -40°C ~ 125°C

- Output frequency range: 35.156MHz ~ 4.5GHz

- Duty ratio: 45 ~ 55%

- Power down mode

- Bypass mode (FOUT = FIN)

- Programmable dividers

- Glitch-free scaler

- On-chip loop filter

- Lock Detector

Block Diagram

Benefits

- Glitch-free scaler

- Low Jitter

- Low Power

Applications

- Mobile/Consumer

What’s Included?

- FE(Front-End) : IPXACT, LEF, LIBERTY, MODEL, TB FUNCTION, TB VECTOR GEN, TWRAP

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| Samsung | 4nm | SF4 | — |

Specifications

Identity

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is Frac-N PLL on Samsung 4nm LN04LPP?

Frac-N PLL on Samsung 4nm LN04LPP is a PLL IP core from SKAIChips listed on Semi IP Hub. It is listed with support for samsung.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.