Ethernet MAC 200G/400G

Size optimized, Silicon agnostic, Silicon Proven Ethernet MAC IP core for High Speed Ethernet applications The 200G/400G Ethernet…

Overview

Size optimized, Silicon agnostic, Silicon Proven Ethernet MAC IP core for High Speed Ethernet applications

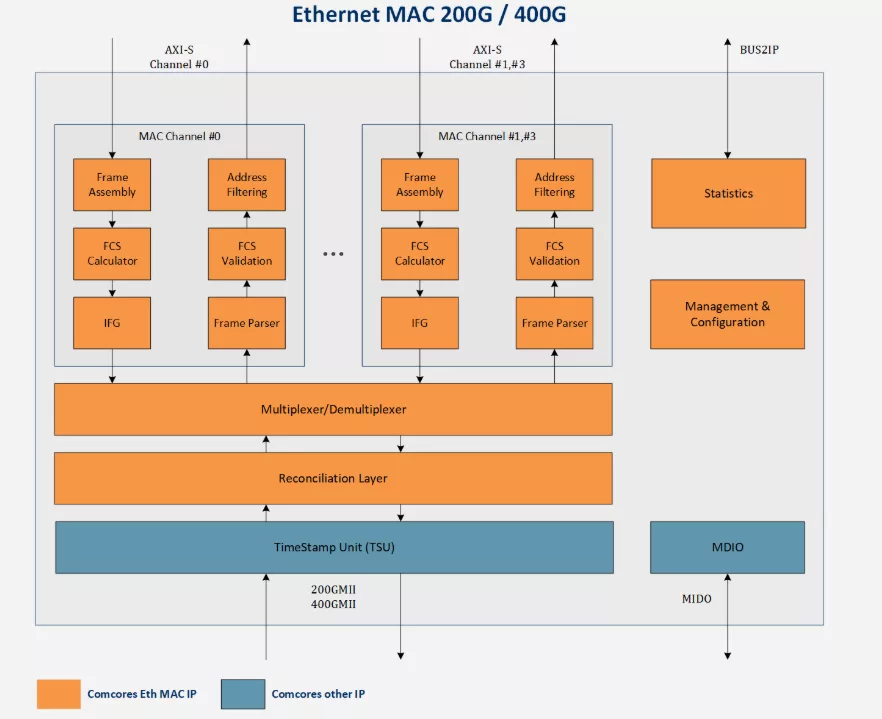

The 200G/400G Ethernet Media Access Control (MAC) IP core provides a comprehensive and flexible solution for implementing the IEEE 802.3 MAC layer for high-speed Ethernet required in demanding applications such as hyperscale data centers, high-performance computing (HPC), and Artificial Intelligence (AI) / Machine Learning (ML) clusters.

Designed for both ASIC and FPGA targets, this IP core enables seamless integration into next-generation networking equipment operating at 200 Gbps and 400 Gbps data rates.

Compliant with the IEEE 802.3 standard, the Comcores MAC IP ensures interoperability while offering features optimized for low latency and high throughput. The core is highly configurable and easy interfacing with Comcores IEEE 1588 Timestamping Unit (TSU) and 40G/100G PCS solutions.

For the client side, the IP cores use a multichannel MAC scheme to guarantee line-speed operation across Ethernet packet sizes. The scheme ensures the packet order is maintained for each MAC channel as well as cross all MAC channels. On the Client side, the core implements two or four 128-bit AXI-S Client interface for 200 Gbps or 400 Gbps operation. A standard 200GMII or 400GMII interface is utilized towards the PHY side.

Key features

Standard Compliance:

- IEEE 802.3bs (200G/400G Ethernet)

- IEEE 802.3 Clause 4 (Reconciliation Sublayer – RS)

- IEEE 802.3 Clause 31 / Annex 31A (Pause Frame Support)

- Supports IEEE 1588v2 Precision Time Protocol (PTP) timestamping (Optional)

- Supports IEEE 802.1Qbb / 802.3bd Priority Flow Control (PFC) (Optional)

- Supports IEEE 802.1Q VLAN tagging, including stacked VLANs

- Data Rates: Configurable for 200 Gbps or 400 Gbps operation

Interface:

- Flexible streaming user-side interface (e.g., AXI4-Stream or native FIFO) with configurable data width (e.g., 512-bit for 200G/400G, 1024-bit for 400G)

- Standard MII interface to PCS layer: 512-bit CDMII (CD = 400 in Latin numerals)

- Standard management host interface (e.g., MDIO Clause 22/45, AXI4-Lite, Avalon-MM) for register access and configuration

Frame Handling:

- Full MAC frame processing (Preamble/SFD generation/detection, FCS insertion/checking/removal)

- Support for jumbo frames (programmable maximum frame length)

- Cut-through operation for reduced latency

- Deficit Idle Count (DIC) for optimized throughput while maintaining average IFG

Flow Control:

- Fully automated IEEE 802.3x Pause frame (XON/XOFF) generation and termination (in non-PFC mode)

- Optional Priority Flow Control (PFC) support (8 classes) for enhanced QoS

Statistics and Monitoring:

- Comprehensive statistics counters for monitoring RMON, MIB-II (RFC 2665), and IEEE 802.3 managed objects

- Counters for various frame types, sizes, errors (Good/Bad Frames, CRC Error, Length Error, Undersize, Oversize, among others)

- Status signals for key events (For example, Local/Remote Fault)

- Optional sideband channel to provide per-frame status/information to the user application

Optimization:

- Optimized for low latency and area efficiency on both ASIC and FPGA platforms

- Optional removal of TX or RX statistics logic to save resources

- Designed for seamless integration with Comcores PCS/FEC IP

- Optional internal MII loopback support.

- Programmable promiscuous mode

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Ethernet MAC 200G/400G?

Ethernet MAC 200G/400G is a Ethernet IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.