ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm

A Wirebond and FlipChip compatible

Overview

A Wirebond and FlipChip compatible <80fF ESD Solutions for Multi-Gigabit SerDes Applications.

This silicon-proven TSMC 28nm Digital I/O Library delivers a low-capacitance, high-reliability interface solution optimized for advanced semiconductor applications. Featuring low-capacitance LVDS differential pairs (<250fF per pin) at 0.8V, this library ensures superior signal integrity for high-speed applications. The I/O macro seamlessly integrates with the TSMC 1.0V I/O Library, sharing a compatible VDDA and VSSA bus structure for streamlined power management. Designed with a 14-bondpad ESD macro, including two differential pairs and dedicated power/ground cells, it provides a robust 0.8V VDDA power domain with a 0V ground reference. Engineered for reliability, the library avoids minimum-width metal traces and adheres to enhanced via/contact recommendations for long-term durability. With Cadence OA database compatibility, the library supports Spectre and auCdl views, enabling seamless simulation, LVS verification, and integration into standard design flows.

Cell List

| Cell Name | Description |

| WD_TXRXMAC_EW | MACRO w/ E/W Poly |

| WD_TXRXMAC_NS | MACRO w/ N/S Poly |

Common Digital PINS

| PIN | Function | Voltage |

| VDDA | 0.8V Core Voltage | 0.8V |

| VDDA | Ground reference & substrate | 0V |

| TX, RX | Low Cap Signal Pad | 0.8V |

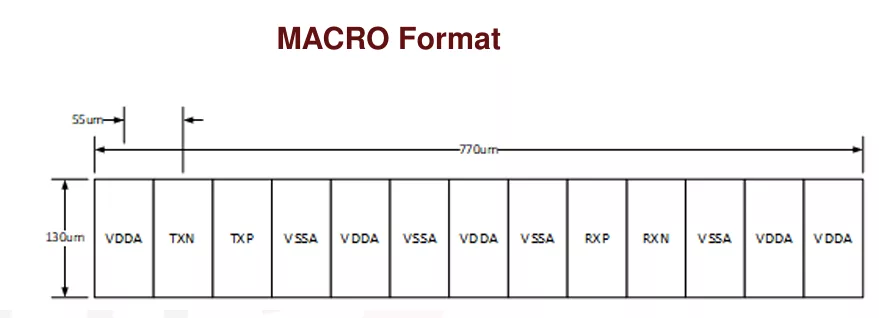

Physical Dimensions

- 14 Bondpads

- 2 Pairs of Low-Cap Signals

- 55um Pitch

- 770um wide and 130um tall

Key features

- Provide Low-Cap Bondpads for differential pair, at a nominal voltage of 0 to 0.8V

- Low Capacitance to be <250fF per pin.

- Designed to intergrate with the TSMC 1.0V I/O Library

- Uses the same VDDA and VSSA bus structures

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | — |

Specifications

Identity

Provider

Learn more about ESD Protection IP core

Maximizing ESD protection for automotive Ethernet applications

Breakthrough in area efficiency of on-chip ESD protection

Designing Electrostatic Discharge (ESD) Protection for Monolithic SoCs and Multi-Die Systems

Selecting optimized ESD protection for CMOS image sensors

Optimized on-chip ESD protection to enable high-speed Ethernet speed in cars

Frequently asked questions about ESD Protection Library IP cores

What is ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm?

ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm is a ESD Protection IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this ESD Protection?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ESD Protection IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.