Master/Slave DLL

The (Delay-Locked Loop) DLL PHY is a mix-signal circuit used in low-power and high-speed applications to align and synchronize cl…

Overview

The (Delay-Locked Loop) DLL PHY is a mix-signal circuit used in low-power and high-speed applications to align and synchronize clock signals with precise timing. This IP ensures robust timing, minimizes skew, and operates efficiently with a small silicon footprint.

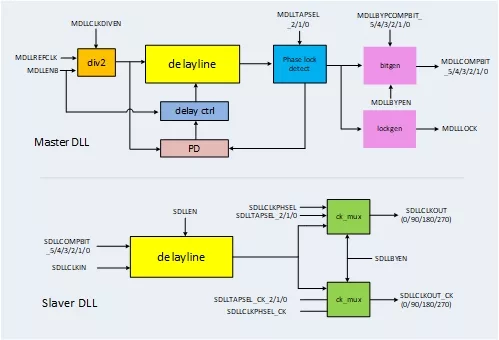

The DLL PHY is designed to generate precise phase-shifted clocks (e.g. 0 ° , 90 ° , 180 °, 270 °) based on a reference clock, enabling high-speed data capture and transmission. It consists of the Master DLL and Slave DLL, each serving specific roles in the clock distribution network.

Key features

- Reference clock frequency range from 200MHz to 800MHz

- Generates accurate phase-shifted clocks (e.g., 0/90/180/270) synchronized with the reference clock

- Optimized for low-power operation

- Ensures proper alignment for high-speed data sampling and transmission

- Provides stable and reliable clock alignment

- Allows customization of delay settings, phase shifts and other parameters to meet specific application requirements

- Designed to mitigate the effects of noise and jitter

- Cycle to Cycle jitter (C2C): ≤150ps

Block Diagram

Benefits

- Low power consumption

- Fully customizable

- High speed hub using VLPI low latency

- Small area

- Simple integration process

What’s Included?

- GDSII

- LVS Spice netlist

- Verilog model

- Synopsys synthesis model

- LEF for clock generator PLL

- User Guidelines

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about DLL IP core

Maximizing Performance & Reliability for Flash Applications with Synopsys xSPI Solution

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Analog Bits and SEMIFIVE is a Really Big Deal

Paving the way for the next generation of audio codec for True Wireless Stereo (TWS) applications - PART 5 : Cutting time to market in a safe and timely manner

The common silicon issues in analog IP integration

Frequently asked questions about DLL IP cores

What is Master/Slave DLL?

Master/Slave DLL is a DLL IP core from Innosilicon Technology Ltd listed on Semi IP Hub.

How should engineers evaluate this DLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.