DiFi IP core

Silicon agnostic, scalable implementation of IEEE-ISTO Std 4900-2021 The DiFi IP core is a scalable and silicon agnostic implemen…

Overview

Silicon agnostic, Highly scalable implementation of IEEE-ISTO Std 4900-2021

The DiFi IP core is a highly scalable and silicon agnostic implementation of the IEEE-ISTO Std 4900-2021: Digital IF Interoperability Standard v1.2.1 targeting ASIC, and FPGA technologies. The DiFi implementation builds on long-time experience designing IP cores for sending and receiving Radio IQ data over Ethernet networks, and delivers a flexible engine that is prepared for tight integration with software applications.

Source (Transmitter) and Sink (Receiver) components are provided, allowing for Duplex Equipment communication and supporting both Uplink and Downlink VITA-49 (VMEbus International Trade Association) stream directions.

DiFi IP from Chip Interfaces is designed to meet or exceed the requirements of stationary or mobile Satellite communication Ground Stations. The speed-optimized core can handle any solutions reaching from the “small footprint” to the most complex applications running on 100G Ethernet links.

Chip Interfaces DiFi IP comes with the widest parameter set available and has gone through extensive testing in our UVM regression test environment.

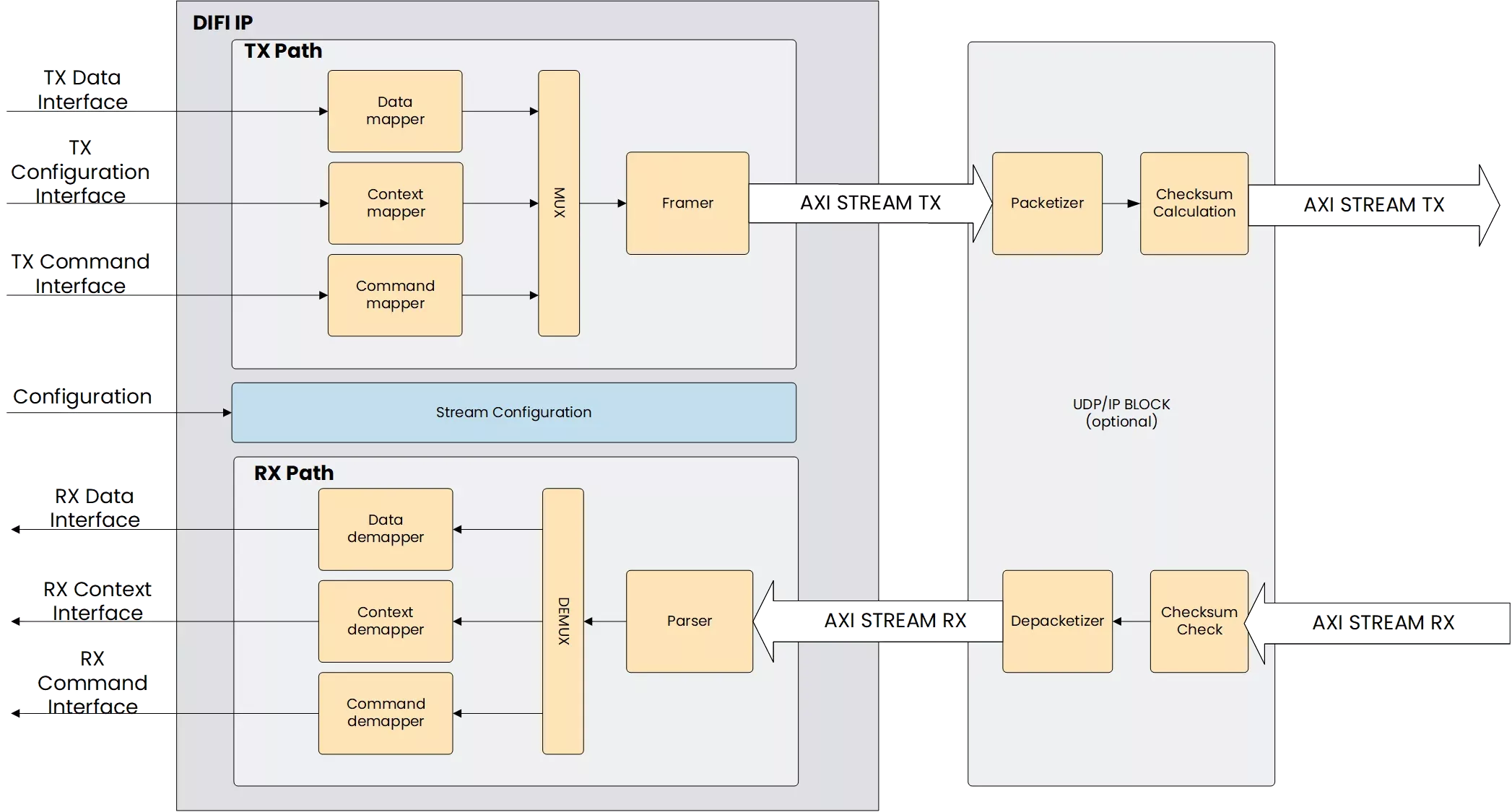

The DIFI IP core interfaces with the UDP IP via the AXI Stream interface, and towards the application with either an AXI MM interface or an AXI Stream interface. The Design consists of both the IF/RF Converter Receive Path and the IF/RF Converter Transmit path, allowing the implementation of both the RF-to-IP and IP-to-RF sides of the communication.

Key features

- Supports: Signal Data, Flow Control, Signal and Version Context Packets

- Integrates Easily with UDP/IP Ethernet Stack through the AXI interface

- Support for all information and packet classes

- Multiple Stream implementation

- Up to 100Gbps Line rates

- Silicon Agnostic

Block Diagram

Benefits

- Test Environment: DIFI IP is Tested in UVM regression for full functional coverage

- Silicon Agnostic: Designed in Verilog and targeting both ASICs and FPGAs

- System Integration: Integration support with Ethernet UDP/IP, MAC and PCS components for quick and efficient deployment

- Active Support: All support is actively provided by engineers directly

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report, Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Optical Transport IP core

Encrypting Telecoms

TPACK's role in Altera designs

Part 2: Opening the 5G Radio Interface

How 224G SerDes Unifies Today’s AI Fabrics

Securing the Future of Terabit Ethernet: Introducing the Rambus Multi-Channel Engine MACsec-IP-364 (+363)

Frequently asked questions about Optical Transport IP cores

What is DiFi IP core?

DiFi IP core is a Optical Transport IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this Optical Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Optical Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.