Deep Buffering Memory 1G Ethernet Switch

switch supporting buffering of large amounts of data in external DDR RAM The 1G deep buffering memory Ethernet Switch is an Ether…

Overview

Advanced switch supporting buffering of large amounts of data in external DDR RAM

The 1G deep buffering memory Ethernet Switch is an advanced Ethernet switching IP that supports buffering large amounts of data in external RAM. The non-blocking Ethernet switch IP core enables fine-grained traffic differentiation for rich implementations of packet prioritization, enabling per port and per queue shaping on egress ports.

The 1G deep buffering memory Ethernet switch IP from Comcores supports MAC learning, VLAN 802.1Q, multicast and broadcast as well as IEEE 1588 transparency. Each port provides a native interface for GMII Ethernet PHY devices.

Key features

Delivers Performance

- QoS features like classification, queuing, and priorities included

- Automatic MAC address learning and aging

- Supports buffering of up to 128 MB in DDR

- Extensive statistic reporting

Highly Configurable

- Buffer size is fully configurable

- Configurable scheduling (round-robin, strict priority, among others)

- Configurable tagging

Easy to Use

- Solid Verification Environment

- Easy integration on Xilinx evaluation platforms

- GMII interfaces for attaching external Physical Layer devices (PHY)

Silicon Agnostic

- Designed in Verilog and targeting both ASICs and FPGAs

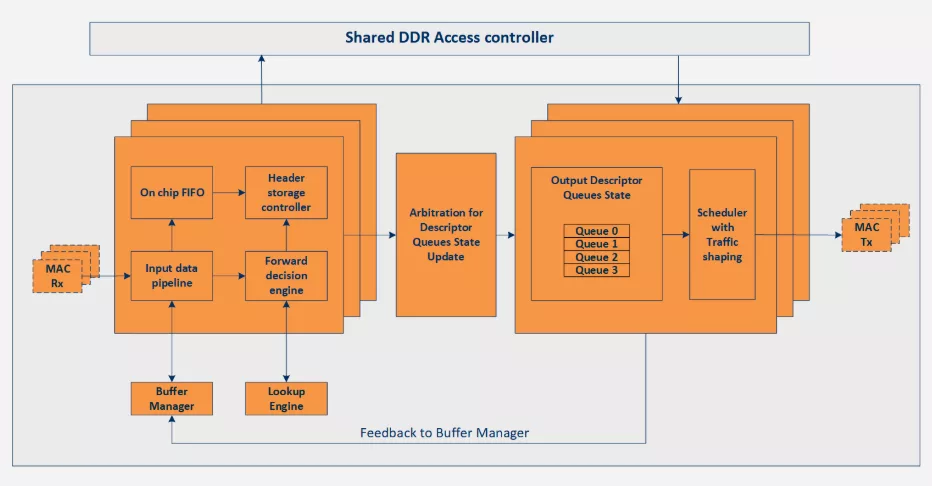

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Deep Buffering Memory 1G Ethernet Switch?

Deep Buffering Memory 1G Ethernet Switch is a Ethernet IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.