High-Definition SMPTE Test Pattern Generator

The HD_SMPTE_TPG IP Core is a versatile test pattern generator capable of producing a range of test patterns in 20-bit 4:2:2 form…

Overview

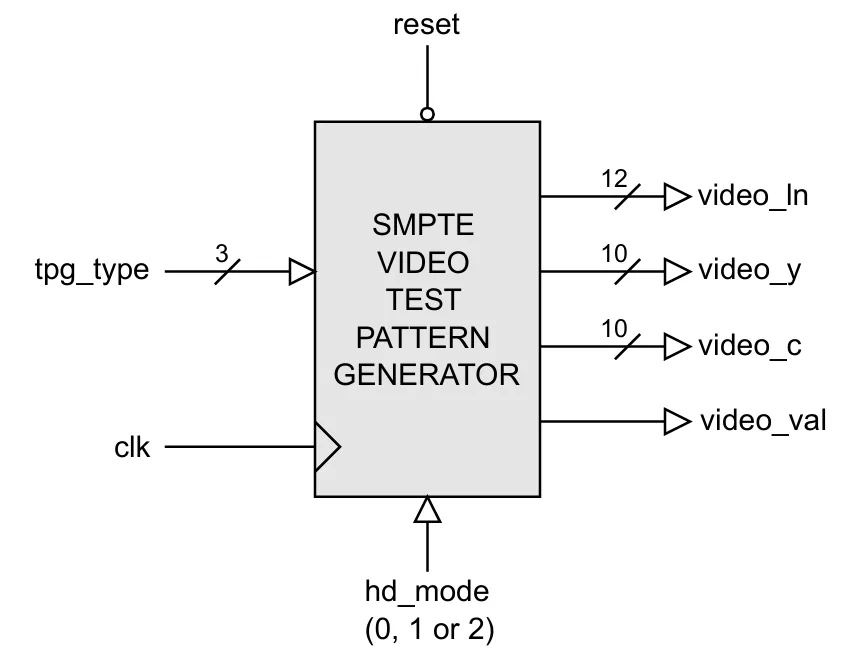

The HD_SMPTE_TPG IP Core is a versatile test pattern generator capable of producing a range of test patterns in 20-bit 4:2:2 format. The output stream format is compliant with the SMPTE standards 296M and 274M. The module is ideal for use in the prototyping stages of digital video systems or as a known good reference source for standard 720p, 1080p or 1080i video.

The video mode is controlled by the generic parameter hd_mode and the video test pattern can be set using the parameter tpg_type. In total there are 8 different test patterns to choose from.

The output video is a standard SMPTE 20-bit stream that is synchronous with the clk signal. The clock frequency should be set to the value that corresponds to the correct pixel clock frequency for the corresponding video mode. For instance, the clock frequency should be set to 74.25 MHz for 720p60, 1080p30 or 1080i60 modes. A clock frequency of 148.5 MHz should be chosen for 1080p60.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human-readable VHDL (or Verilog) source code

- Test patterns generated as an industry standard 20-bit 4:2:2 SMPTE stream

- YCbCr 4:2:2 output pixels

- All 720p, 1080p and 1080i video formats supported (SMPTE 296M and SMPTE 274M)

- Colour-bar output with choice off 8 different patterns

- All signals synchronous with the pixel clock

- Compatible with a wide range of video encoder ICs

- Tiny implementation size makes the core suitable for even the smallest FPGAs and CPLDs

Block Diagram

Applications

- Digital video testing and prototyping

- Default output displays and simple 'screen savers'

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is High-Definition SMPTE Test Pattern Generator?

High-Definition SMPTE Test Pattern Generator is a Video Processing IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.