DVB-C Demodulator

The demodulator is designed to be used together with a cable tuner and an analog to digital converter (ADC).

Overview

The demodulator is designed to be used together with a cable tuner and an analog to digital converter (ADC).

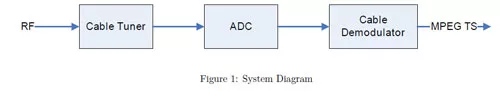

The system has an internal state machine to control the operation, which can be externally configured via the SPI interface. A typical system application is shown in Figure 1.

This DVB-C QAM demodulator is supplied as a portable and synthesizable Verilog-2001 IP. The system is designed to be used in conjunction with a standard cable tuner. The QAM signal is acquired blindly, and QAM signal constellations from QAM 16 through QAM 256 are supported. The operation of the demodulator is automated by a master finite state machine.

Key features

- DVB-C EN 300 429 & ITU-T J.83 Annex A & Annex C compliant QAM demodulator

- Supports IF input

- QAM constellations 16, 32, 64, 128 and 256

- Symbol rates up to 7 MBaud

- Blind acquisition of QAM constellation sizes

- Parallel and Serial MPEG outputs

- 3 external clocks, or 2 external, 1 internally generated

- SPI port (Slave) to external processor

Block Diagram

Applications

- Set-top boxes

- Cable receivers

- Digital cable ready TV sets

What’s Included?

- Synthesizable Verilog-2001

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

- FPGA testing environment

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Modulation Demodulation IP core

Three Major Inflection Points for Sourcing Bluetooth Intellectual Property

Part 2: Opening the 5G Radio Interface

An Integrated, Tunable RF Filter: an Enabler for Reconfigurable Front-Ends

Design considerations for integrated CMOS receivers

Silicon IP for Programmable Baseband Processing

Frequently asked questions about Modulation and Demodulation IP cores

What is DVB-C Demodulator?

DVB-C Demodulator is a Modulation Demodulation IP core from WASIELA listed on Semi IP Hub.

How should engineers evaluate this Modulation Demodulation?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Modulation Demodulation IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.