CXL Verification IP

CXL Verification IP provides an smart way to verify the CXL bi-directional bus.

Overview

CXL Verification IP provides an smart way to verify the CXL bi-directional bus. The SmartDV's CXL Verification IP is fully compliant with Compute Express Link Revision 1.0, 1.1 and 2.0 Specification and provides the following features.

CXL Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

CXL Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports CXL specs revision 1.0, 1,1 and 2.0.

- Supports Native PCIe mode and below features as defined in the PCIe specification.

- PCIE Express specs 1.0/2.0/3.0/4.0/5.0/5.1

- Serial, PIPE, PCS/PMA, Low pin count and SerDes interface

- Link Width negotiation

- Up configure, polarity inversion, and lane-to-lane skew

- Configurable Spread Spectrum Clocking (SSC)

- ASPM and Software controlled Power Management

- Supports configuration of PCIe vs CXL protocol mode.

- Supports the signaling rate of 32 GT/s, degraded rate of 16 GT/s or 8 GT/s in CXL mode.

- Supports Link width support for x16, x8, x4, x2(degraded mode), and x1(degraded mode) in CXL mode.

- Bifurcation (aka Link Subdivision) support to x4 in CXL mode.

- CXL.io, CXL.mem, and CXL.cache support.

- Supports ARB/MUX Link Management Packets(ALMP).

- Supports CXL Power Management VDM Packets.

- Supports arbitration and data multiplexing/demultiplexing.

- Supports following CXL.cache/CXL.mem slots,

- Header slot

- Generic request/response slot

- Generic data slot

- Supports following CXL cache line,

- 32B Half cache line

- 64B Full cache line

- Supports following CXL flit type encoding,

- Protocol type

- Control type

- Supports all CXL.cache/CXL.mem request and response messages.

- Supports all snoop responses.

- Supports various framing errors.

- Supports Multiple Data Header(MDH).

- Supports byte enable.

- Supports CXL.cache/CXL.mem link layer retry.

- Supports type 1, type 2 and type 3 CXL Devices.

- Supports implied EDS token.

- Supports Address Translation Service(ATS).

- Supports configurable TC to VC queue mapping.

- Supports data poisoning.

- Supports virtual channel management.

- Support for upto 4K payload size and 256 functions.

- Supports Type 3 Multi Logical Device components.

- Supports CXL 1.1 and 2.0 Control and Status Registers.

- Supports CXL Error VDM Format.

- Supports Cache Requests as per Buried Cache State Rules.

- Supports QoS Telemetry for Memory.

- Supports Advanced Error Reporting (AER).

- CXL devices supports three types of resets

- Hot Reset

- Warm Reset

- Cold Reset

- Supports Memory Interleaving process.

- Callbacks in Host, Device and monitor for user processing of data.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- CXL Verification IP comes with complete testsuite to test every feature of CXL specification.

- Functional coverage for complete CXL features.

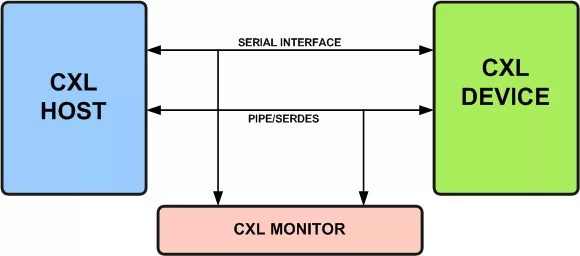

Block Diagram

Benefits

- Faster testbench development and more complete verification of CXL designs.

- Easy to use command interface simplifies testbench control and configuration of Host and Device.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the CXL testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is CXL Verification IP?

CXL Verification IP is a CXL IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.