Cross-Correlator With 64x2 Channels

PMCC_XCM_64x64 is an IP block capable of calculating the cross-correlations between 64x2 analog signals supplied to the inputs AR…

Overview

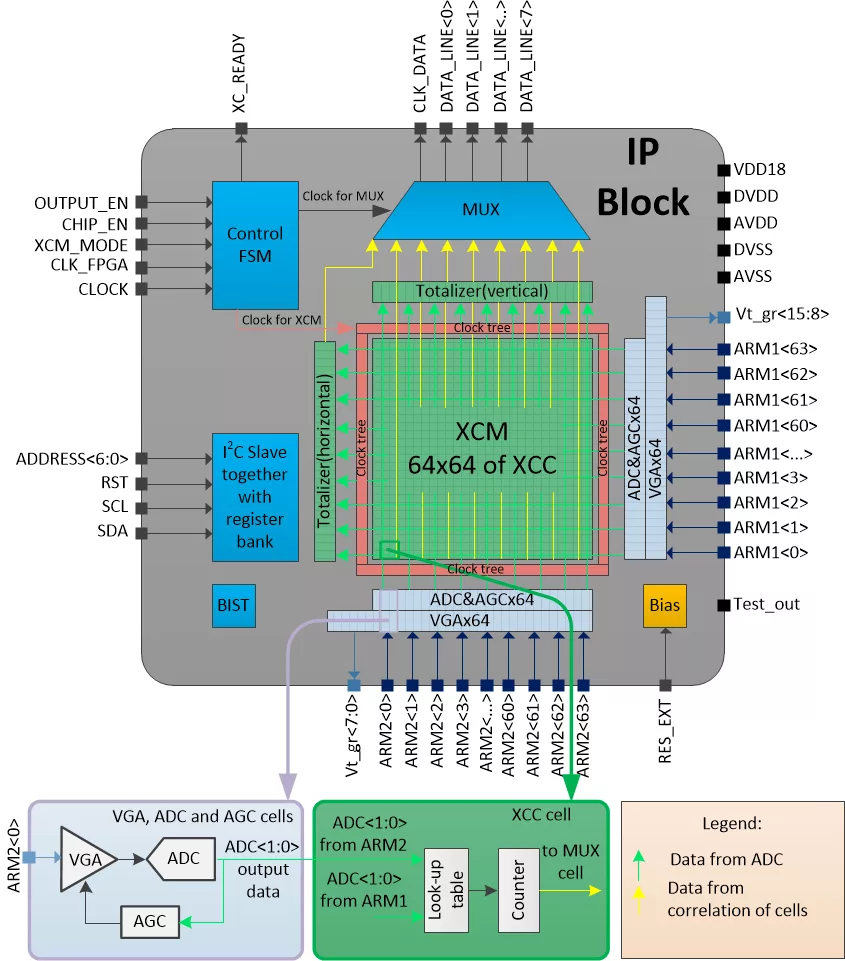

PMCC_XCM_64x64 is an IP block capable of calculating the cross-correlations between 64x2 analog signals supplied to the inputs ARM1<63:0> and ARM2<63:0>. The IP block operates sequentially in two modes: integration and data readout. During the integration mode, the IP block calculates cross-correlation between the signals for a preset period of time. During the data readout mode, the IP block prepares the data and transmits it to the 8-bit output multiplexer.

Analog signals from inputs ARM1 and ARM2 with the bandwidth from 10 MHz to 500 MHz are passed through the variable gain amplifiers (VGAs) to the 2-bit A/D converters. An automatic gain control (AGC) circuit is using the 2-bit data to adjust the input signal level at the ADC’s input through adjusting the VGA’s gain. The AGC loop controls the VGA gain in such a manner that the average duty cycle of the ADC’s LSB would be equal to 0.7 by default.

The data from the ADC block is passed to the main functional block of the cross-correlator IP – the Cross- Correlation Matrix. This block is responsible for crosscorrelation of 64 2-bit signals from one arm with 64 2-bit signals from another arm. The matrix consists of 4096 crosscorrelation cells, 64 vertical totalizers and 64 horizontal totalizers. The cross-correlation cell (XCC) consists of the multiplication and accumulation blocks. The power consumption of a single correlation cell is minimized to ensure high power efficiency of the IP block.

A Totalizer consists of an array of adder cells which count the number of occurrences of each possible two-bit input values supplied from the A/D converter.

An Output Multiplexer (MUX) performs serializing of the data stored in Cross-Correlation Cells and Totalizer Cells. The I2C Interface is built in for the IP block’s control.

Key features

- 64x2 single-ended inputs with on-chip termination

- Computed correlation between a pair of two-bit inputs, “a” and “b”:

- a, b ? {-3, -1, 1, 3}

- a×b => {-9, -3, -1, 1, 3, 9}

- ÷ 3 => {-3, -1, 0, 0, 1, 3}

- + 3 => {0, 2, 3, 3, 4, 6}

- 1 GHz clock signal

- Input clock delay adjustment

- 10MHz to 500MHz input signal frequency

- range

- Adjustable VGA input termination 50?/100?/200?/Hi-Z for interconnection of several IP blocks on-board

- -20dBm to -10dBm input power level range

- Zero-crossing comparator offset correction

- Adjustable ADC conversion range

- Additional clock input for the cross-correlator matrix readout

- Implemented 10ms on-chip integration time

- Programmable integration and reading time

- Serialized 8 bit output data

- Tristate output buffers

- Less than 0.1mW power per correlation cell

- I2C control interface up to 1MHz

- BIST

- Radiation hardened (TID immune latch-up free) process

- Compatible with a BGA289 package

Block Diagram

Benefits

- PMCC_XCM_64x64 is an IP block capable of calculating

- the cross-correlations between 64x2 analog signals.

Applications

- Spectrometers and radiometers

- Synthetic aperture radars

- Complex meteo analyzers

- Digital phase detectors

What’s Included?

- GDSII file

- Netlist for Spectre simulation

- Layout and Schematic (DRC & LVS) verification reports

- Complete IP block’s datasheet with integration/application notes

- Optional deliverables are:

- Library containing an entire hierarchy of the IP block’s schematic and layout cells

- Extracted views containing parasitic components from layout

- Verilog-A model replicating the IP block’s functionally

- Simulation test-benches

- Optional components specific to the IP block: biasing, specialized I/Os, glue-logic, transmission lines etc.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is Cross-Correlator With 64x2 Channels?

Cross-Correlator With 64x2 Channels is a Filters Transforms IP core from Pacific MicroCHIP Corp. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.