2.56 MHz Digital filter

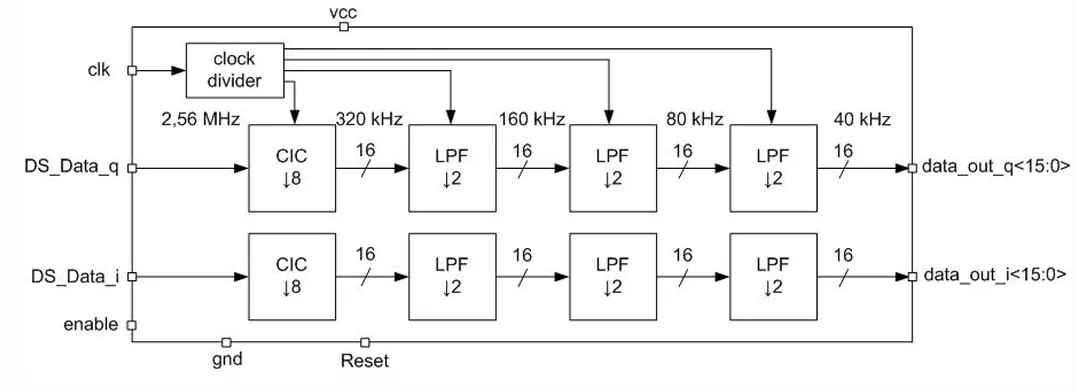

The block consists of 4 low pass filters connected in serially.

Overview

The block consists of 4 low pass filters connected in serially.

Decimation takes place during a filtration process after each stage. The total decimation coefficient is 64.

The block is fabricated on iHP SiGe BiCMOS 0.25 um (SGB25V) technology.

Key features

- SGB25V technology

- Build-in clock former

- Test modes – digital data output

- Operating with complex signal

- Low current consumption: 80 uA at the input sampling rate 2.56 MHz

- Input data - the delta-sigma modulated signal

- Small area: 1.4 mm2 on iHP SGB25V technology and supply voltage is 1.8 V

- Portable to other technologies (upon request)

Block Diagram

Applications

- Delta-sigma ADC

- Systems using a delta-sigma modulator signal as an input data

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is 2.56 MHz Digital filter?

2.56 MHz Digital filter is a Filters Transforms IP core from NTLab listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.