CCSDS 121/123 Lossless Compression

The GRSHYLOC IP enables lossless compression for multi-spectral and hyper-spectral images according to the CCSDS121 and CCSDS123 …

Overview

The GRSHYLOC IP enables lossless compression for multi-spectral and hyper-spectral images according to the CCSDS121 and CCSDS123 standards.

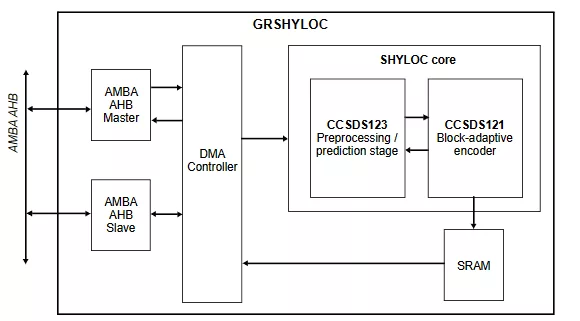

The IP features a DMA engine to fetch the raw image and store the compressed bitstream from/to external memory through the AMBA AHB master interface.

GRSHYLOC implements a wrapper for the SHYLOC compressor, enabling two possible configurations by means of a generic. Both configurations have common control and data interfaces. The compressed samples are temporary stored into a local SRAM. This reduces the risk of missing output data in case of delays accessing the AHB bus. The content of the memory is written to the external memory when the DMA controller is not busy fetching raw data for the SHYLOC core. GRSHYLOC also includes an AMBA AHB slave interface for configuration and control. There are three sets of registers: one for configuring the CCSDS123 IP, another for the CCSDS121 encoder (optional) and a global set for controlling the overall compression process.

The block diagrams show the two possible configurations for GRSHYLOC. The first one involves the complete SHYLOC system: the CCSDS123 IP performs the prediction stage, whereas CCSDS121 implements the block-adaptive coding. On the other hand, the second configuration only instantiates the CCSDS123, which performs both as predictor and as sample-adaptive encoder.

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Data Compression IP core

Data compression tutorial: Part 3

Firmware Compression for Lower Energy and Faster Boot in IoT Devices

A configurable FPGA-based multi-channel high-definition Video Processing Platform

IP Core for an H.264 Decoder SoC

Digital Associative Memories Based on Hamming Distance and Scalable Multi-Chip Architecture

Frequently asked questions about Data Compression IP

What is CCSDS 121/123 Lossless Compression?

CCSDS 121/123 Lossless Compression is a Data Compression IP core from Frontgrade Gaisler listed on Semi IP Hub.

How should engineers evaluate this Data Compression?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Data Compression IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.