Avalon Mobile DDR Memory Controller

The Microtronix Avalon Mobile DDR SDRAM Memory Controller IP Core is designed for building high-performance Avalon-MM / Avalon-ST…

Overview

The Microtronix Avalon Mobile DDR SDRAM Memory Controller IP Core is designed for building high-performance Avalon-MM / Avalon-ST multi-master streaming data systems. Advanced design features enable maximum system clock rates using low speed FPGA's and standard memory devices lowering your production cost, and saving you money.

The core support single or multi-port configurations which are configured via a user friendly GUI interface. Using mutiple ports, the system design architecture can be partitioned into separate daya busses each independently clocked to achieve maximum preformance. The ports contain a configurable data FIFO used to buffer streaming data and effectively doubling memory bandwidth on sequential address hits.

The core is optimized for Altera® Cyclone, Stratix and Arria GX families of field programmable logic devices and supplied with an easy-to-use Quartus® SOPC Builder Ready component.

Key features

- 200 MHz Cyclone / Stratix memory performance

- Supports all standard Mobile DDR SDRAM devices

- 1 to 16 Avalon® independent local bus port interfaces

- Avalon Pipelined and Burst transfers

- Avalon-MM local bus width from 8 to 128-bits

- Altera SOPC Builder Ready & Qsys Configuration GUI simplifies timings

- Integrates seamlessly into Avalon-ST video framework

- Automatic generation of initialization and refresh sequences

- MDDR deep power-down

- Memory data width: 8/16/32/64-bit

- Intelligent SDRAM burst caching controller minimizes wait-states

- Multiple time domain clocking of ports and memory

- IP supports: Cyclone II, III, IV, V, Stratix I, II, II-GX, III, IV/IV GX and Arria GX, II-GX

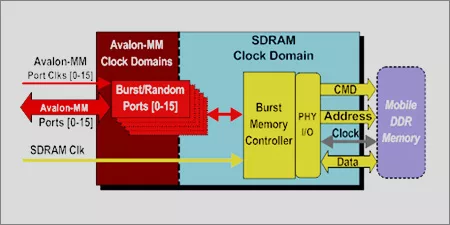

Block Diagram

Benefits

- Source synchronous MDDR clocking simplifies timing closure

- PCB layout independent DDR Round-Trip capture scheme

- Configurable port FIFO maximizes performance of streaming data applications

- Configurable memory and local bus data width optimizes system cost

- System/memory independent time domain clocking optimizes performance

- Round-robin (default) and user defined bus arbitration schemes

- On Die Termination (ODT) support improves signal integrity

What’s Included?

- Altera SOPC Builder Ready & Qsys Configuration GUI

- TimeQuest timing analyzer Synopsis Design Constraint file

- VHDL IP functional simulation models

- Altera OpenCore Plus evaluation license available

- License Options

- Node Locked: Supports a single user. It is tied to the NIC ID of a PC.

- Floating Server: Supports multiple users, typically 1, 2 or 5 seats

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Controller IP cores

What is Avalon Mobile DDR Memory Controller?

Avalon Mobile DDR Memory Controller is a DDR IP core from Microtronix Datacom Ltd. listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.