AHB Low Power Subsystem - ARM Cortex M0

The AHB Low Power Subsystem is an AMBA® based system that is useful as the basic digital infrastructure for building low power SO…

Overview

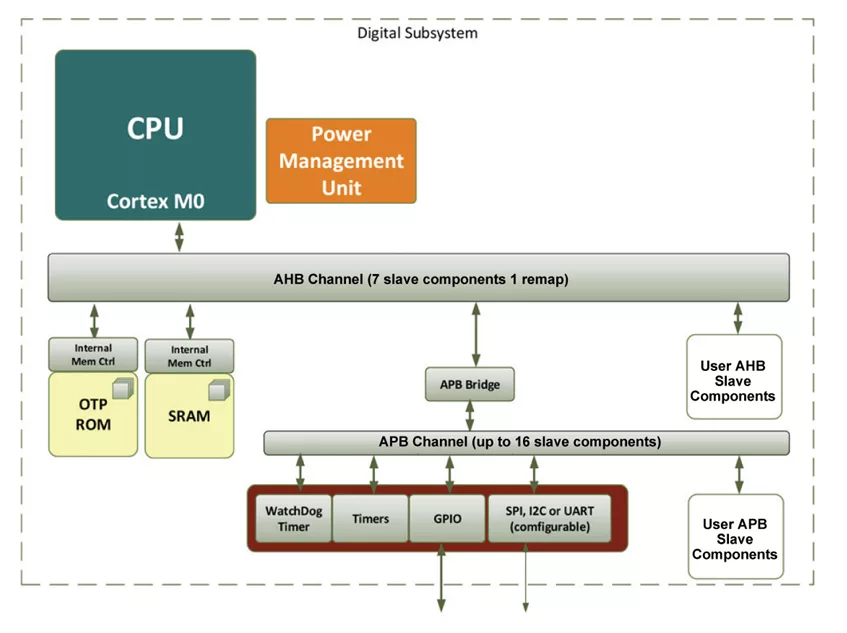

The AHB Low Power Subsystem is an AMBA® based system that is useful as the basic digital infrastructure for building low power SOCs. The subsystem contains a flexible Power Management Unit that controls the power sequence of the CPU as well as the APB peripherals. The PMU can easily be extended to control additional cores, peripherals and even mixed signal subsystems on the same SOC.

The AHB Low Power Subsystem includes a standard set of peripherals and cores that supports RTOS and software kernels. The package includes software for boot code, interrupt handlers and driver code.

The AHB Low Power Subsystem is soft IP that can be used in all the popular semiconductor technology nodes.

Key features

- Low Power

- RTOS/Kernel Support

- AMBA AHB 2.0

- AMAB APB 3.0

- Power Management Unit

- Multiple Power Domains

Block Diagram

Benefits

- Quick design start

- Integration expertise and support

- Hardware/Software and application support

- Cost effective

Applications

- IoT Edge Devices

- Small Controllers

- Mixed Signal Digital - MEMS

- Smart Sensors

- Smart Lighting

- Health Monitors

- Power Management

- Industrial Sensors

What’s Included?

- Verilog RTL source code

- Test bench with test suites

- Documentation including User's Guide and Integration Guide

- Technology-independent synthesis constraints

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is AHB Low Power Subsystem - ARM Cortex M0?

AHB Low Power Subsystem - ARM Cortex M0 is a CPU IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.