32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA.

InCore Calcite is a 32/64 Bit RISC-V in-order, single-issue 5-stage pipelined micro-processor.

Overview

InCore Calcite is a 32/64 Bit RISC-V in-order, single-issue 5-stage pipelined micro-processor. Built on Incore's proprietary deep-customization stack for microarchitectural exploration, Calcite delivers an optimal balance between power and performance in an exceptionally small silicon footprint.

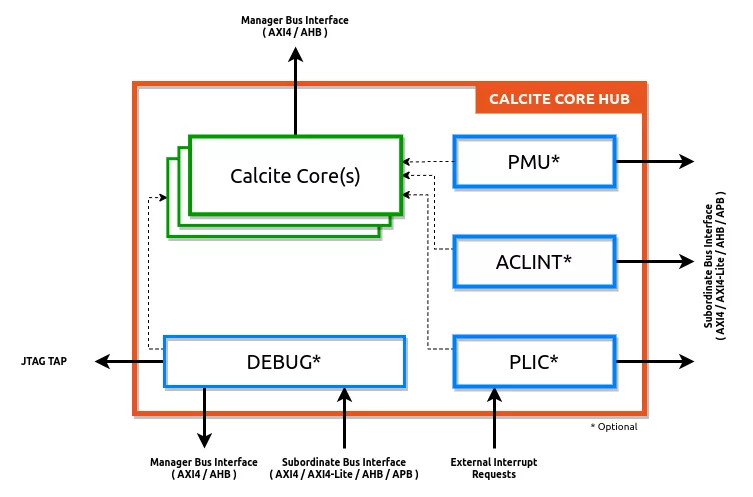

The Calcite core comes bundled as a compute subsystem, with integrated AMBA protocol interconnects (supports AXI4, AHB) and uncore components (PMU, debug, interrupt controllers etc).

Key features

- An in-order 5-stage 64/32-bit processor

- Supports RISC-V ISA: RV[64|32]IMAFDCSU [HBP]

- Single issue

- Targets mid-range compute systems: 500-800MHz

- Supports RISC-V Linux, secure L4

- Variants for low-power and high-performance

- Positioned against ARM Cortex A5/A35

- MMU and PMP support

- Single and Double Precision Floating point units compliant with IEEE-754

- Supports the OpenOCD based debug environment through JTAG

- Non-invasive Debug architecture

Block Diagram

Benefits

- Configurability

- Over 2000 optimal design points

- Custom RISC-V extensions supported

- Time to Market

- Compute subsystem (core, interconnect, uncore) to quick-start SoC development

- PPA

- Industry-beating performance and area

Applications

- Linux Devices

- Consumer Electronics

- IoT

- Wearables

- Terminals

- Multimedia

- IP Camera

- Storage Controllers

- Mixed Signal Embedded

What’s Included?

- RTL (Verilog)

- Fully synthesizable

- Human-readable

- Documentation:

- Datasheet

- User Guide

- Integration Guide

- Architecture Reference Guide

- Programmer's Guide

- Hardware Development Kit (HDK):

- FPGA: Xilinx bitstream

- Verification test suites

- ASIC: Synthesis and Constraints scripts

- Software Toolchain:

- GCC Cross Compiler

- GDB

- Open OCD

- Assembler

- Disassembler

- Linker

- Instruction Set Simulator

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA.?

32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA. is a CPU IP core from InCore listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.