JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor

JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor provides a smart way to verify the JTAG component of a SOC or a ASIC in Emulat…

Overview

JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor provides a smart way to verify the JTAG component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor is fully compliant with standard JTAG Specification and provides the following features.

Key features

- Follows JTAG basic specification as defined in JTAG Specification 3

- Supports Jtag protocol standard IEEE 1149.1 and IEEE 1149.6

- Supports all the JTAG tap instructions

- Supports programmable clock frequency of operation

- Supports checks for following

- Check-points include Initialization rules

- State based rules,Active Command rules

- Read/Write to Instruction and data register Rules

- Supports instruction register and data register of size up to 64 bits

- Supports proficiency to extend with user defined instructions and registers

- Has ability to read BSDL file and

- Automatically generate testvectors to test all BSDL cell types

- Automatically generate SVA assertions properties

- Supports all types of timing and protocol violation detection

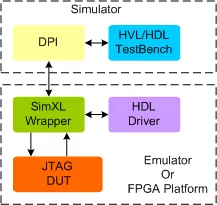

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the JTAG (IEEE 1149.1/1149.6) testcases

- Examples showing how to connect and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Test / Debug IP core

Metric Driven Validation, Verification and Test of Embedded Software

Tools for Test and Debug : Embedded designers face a myriad of multiprocessor challenges

Securing Scale-Up AI: Cadence’s Complete UALink Solution

eUSB2V2: Trends and Innovations Shaping the Future of Embedded Connectivity

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Frequently asked questions about SerDes Test / Debug IP cores

What is JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor?

JTAG (IEEE 1149.1/1149.6) Synthesizable Transactor is a Test / Debug IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Test / Debug?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Test / Debug IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.