Overview

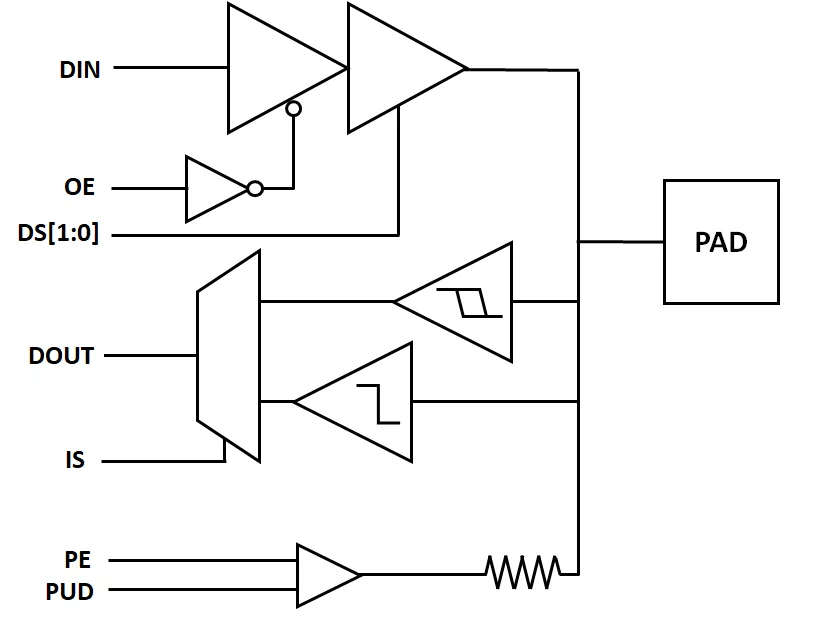

This 28nm GPIO is designed for high-speed (>150MHz output, >250MHz input) applications. The IO operates at either 1.8V or 3.3V and can dynamically switch between these voltages during operation. The cell is power sequence-independent and is fully self-protecting during the power ramp. A unique feature of the 28nm GPIO is its fail-safe capability. Though a full push-pull IO, the part can be powered down and leak low current from externally driven active signals, much like an open-drain IO.

Built into our IO libraries and also offered as a separate service is our strong ESD expertise. Certus was founded by ESD engineers, and our results speak for themselves. We consistently exceed 2KV HBM and 500V CDM ESD targets and provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD, and Cable Discharge Events (CDE).

Certus supports IO libraries across multiple TSMC nodes, including 180nm, 130nm, 40nm, 28nm, 22nm, and 16/12nm. Certus is particularly suited at providing custom variants in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

Learn more about Oscillator IP core

In this paper, we present a flexible ring oscillator IP designed for a 40nm CMOS technology, whose oscillation frequency can be chosen from 200kHz to 20MHz. It was developed using a new design approach, in which analog IPs are designed from scratch to be flexible, employing modular blocks that can be easily customized. The IP is silicon proven. It works with a supply voltage of 1.2V and features 5% frequency accuracy, occupying an area of 0.0022mm2.

This article outlines Key ASIC R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

This article outlines our R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

How do you ensure that every part of a system receives the clock it needs—without wasting power or sacrificing performance? The answer lies in creating a well-structured frequency plan built around a PLL.

Agile Analog’s tamper detection IP is a comprehensive set of sensors and monitors designed to detect a wide variety of physical attacks and side-channel attacks (SCAs). T

Unfortunately, precise thermal monitoring reached an inflection point at 2nm, with traditional solutions proving less practical below 3nm. To tackle the issue, this article delves into a novel approach, accurate to ±1.0°C, that overcomes this critical challenge.