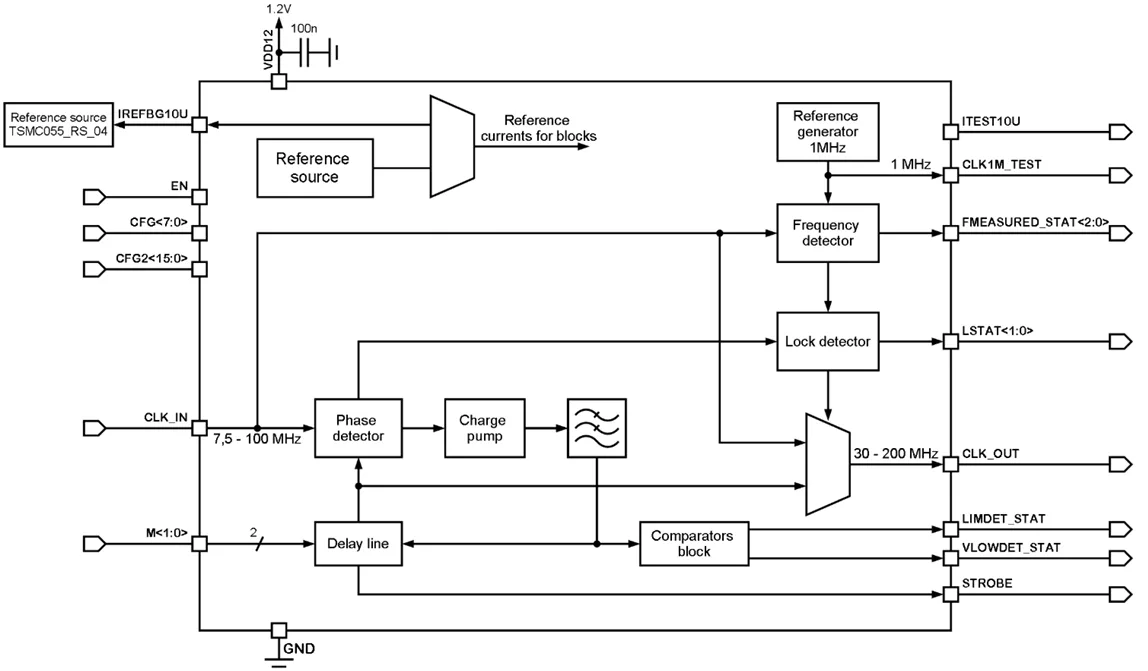

30-200 MHz DLL-based frequency multiplier

055TSMC_DLL_01 is a frequency multiplier that combines low phase jitter of clock signal, small area and low current consumption.

Overview

055TSMC_DLL_01 is a frequency multiplier that combines low phase jitter of clock signal, small area and low current consumption. Block wakes up in “pass-through” mode and passes the input signal to the output. Once configured and enabled the block waits until DLL locks and then switches output clock signal CLK_OUT to higher frequency. Disabling block switches it back into “pass-through” mode. Any mode switching is glitch-protected.

Key features

- TSMC CMOS 55 nm

- 30 – 200 MHz output frequency

- 7.5 – 100 MHz reference frequency

- Multiplication factor 1, 2, 3 or 4

- Glitch-free mode switching

- DLL lock indication

- Easy to configure

Block Diagram

Applications

- Digital circuit clocking

- Frequency synthesizers

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 55nm | GP | Pre-Silicon |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about DLL IP core

Maximizing Performance & Reliability for Flash Applications with Synopsys xSPI Solution

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Analog Bits and SEMIFIVE is a Really Big Deal

Paving the way for the next generation of audio codec for True Wireless Stereo (TWS) applications - PART 5 : Cutting time to market in a safe and timely manner

The common silicon issues in analog IP integration

Frequently asked questions about DLL IP cores

What is 30-200 MHz DLL-based frequency multiplier?

30-200 MHz DLL-based frequency multiplier is a DLL IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Pre-Silicon.

How should engineers evaluate this DLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.