What is 16-Bit xSPI PSRAM PHY?

16-Bit xSPI PSRAM PHY is a Semiconductor IP IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

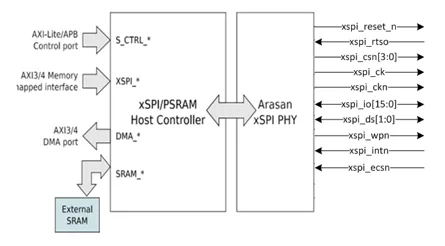

Arasan’s xSPI/PSRAM interface PHY is designed to work with both the xSPI or PSRAM master host controller IPs.

Arasan’s xSPI/PSRAM interface PHY is designed to work with both the xSPI or PSRAM master host controller IPs.

When coupled with the ACS xSPI/PSRAM PHY, the combined IPs are able to interact with SPI, Dual SPI, Quad SPI, Octal SPI, xSPI and 16-bit PSRAM devices at the 500Mb/s data rate per line (250MHz dual rate clock). This includes both HyperRAM and HyperFlash protocols. Both single and dual data rate modes are supported. The xSPI Master controller IP supports flash devices, whereas the xSPI/PSRAM controller has been designed to support SRAM types of devices using the same interface.

Note: some files may require an NDA depending on provider policy.

16-Bit xSPI PSRAM PHY is a Semiconductor IP IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Semiconductor IP IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.