128-Point FFT/IFFT IP Core

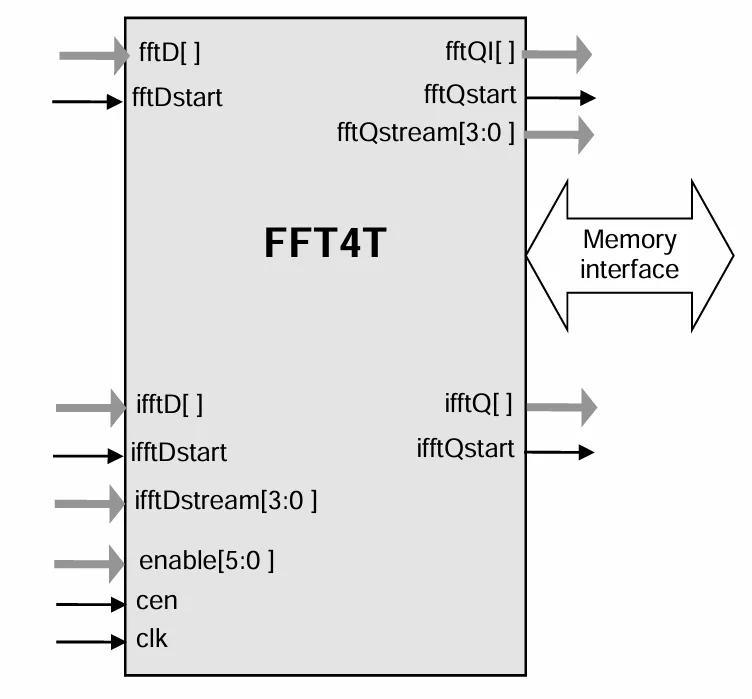

The FFT4T core implements a 128 point complex FFT and IFFT over 12 data streams in hardware.

Overview

The FFT4T core implements a 128 point complex FFT and IFFT over 12 data streams in hardware. It runs at the clock frequency four times higher than the insput sampling frequency.

FFT4T core is a specialized FFT/IFFT processor intended for a situation where an RF signal is recieved over multiple channels in parallel and its filtering is to be performed in the frequency domain. The core fits nicely into, for example, a multichannel GPS system.

Pin Description

| Name | Type | Description |

| CLK | Input | Core clock signal(4x sample clock) |

| Cen | Input | Synchronous enable signal. When LOW the core ignores all its inputs and all its outputs must be ignored. |

| enable[5:0] | Input | RF band enable signals. Each bit controls two streams (path A and path B).

|

| fftD[] | Input |

Input of FFT, Multiple samples in parallel, one for each stream. The samples shall be clocked in on the sample clock. |

| fftDstart | Input | HIGH pulse clocked on the sample clock indicates the initial 0 sample of the 128-sample frame of fftD |

| fftQ[ ] | Output |

Output of the FFT, multiple samples in parallel. Each stream is output contiguously on sequential sample clocks |

| fftQstart | Output | HIGH pulse on sample clock marks the first word of fftQ output (n = 0, samples 0..15) for the stream |

| fftQstream[3:0] | Output | The value between 0 and 11 indicates the stream number |

| ifftD [ ] | Input |

Input of the IFFT, Multiple samples in parallel. Each stream is clocked in put contiguously on sequential sample clocks. |

| fftDstart | Input | HIGH pulse clocked on the sample clock indicates the start of the 128 sample frame (n = 0, samples 0..15) for the stream |

| fftDstream[3:0] | Input | The value between 0 and 11 indicates the stream number |

| fftQstart | Output | HIGH pulse on the sample clock indicates the initial 0 sample of the 128 sample frame of fftD path A streams |

| fftQ[ ] | Output |

Output of IFFT, 12 samples in parallel, one for each stream. The samples shall be clocked on sample clock. |

Key features

- Supports 128-point complex streaming FFT and IFFT operating simultaneously

- Input and output data are in the natural order

- Multiple streams on input, with optional offset by using a 50% (64 samples) overlap.

- Throughput of 1 sample (In-phase I + quadrature Q) per sample clock for each of the input streams; no gap processing of the input data

- Input of FFT and output of IFFT are parallel streams (multiple samples, one for each of the streams in parallel)

- Output of FFT and input of IFFT are per-stream, multiple samples in parallel.

Block Diagram

Applications

- Signal Analysis

What’s Included?

- Synthesizable Verilog RTL source code

- Bit-accurate software model

- Simulation scripts

- Self-checking Test environment

- Test-bench

- Test-vectors

- Expected results

- Synthesis scripts

- User Manual

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is 128-Point FFT/IFFT IP Core?

128-Point FFT/IFFT IP Core is a Filters Transforms IP core from IP Cores, Inc. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.