The FastMath Pack is a math processing accelerator for the ARC HS family

The ARC® HS3x processors, which include the HS34, HS36 and HS38, are based on the -efficient ARCv2 instruction set architecture (…

Overview

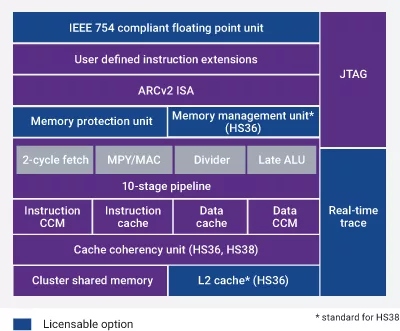

The ARC® HS3x processors, which include the HS34, HS36 and HS38, are based on the highly-efficient ARCv2 instruction set architecture (ISA) and pipeline that deliver a high degree of performance efficiency and code density with minimal power and area for embedded applications. The ARC HS3x processors can be configured as dual core or quad core for maximum performance.

The HS34 processor is optimized for use in high-end embedded applications where real-time, deterministic response is desired, such as SSD controllers, baseband control, digital TV, home networking, automotive systems and smart appliances.

The HS36 processor has all the features of the HS34 and adds support for up to 64KB of instruction and data cache. The HS36 processors is ideally suited for high-performance embedded applications such as SSD controllers, networking, medical, and industrial & automotive systems.

The ARC HS38 processors is optimized for use in high-performance embedded applications running Linux. The processor has a full-featured Memory Management Unit (MMU) supporting a 40-bit physical address space and page sizes up to 16 megabytes (MBs), giving designers the ability to directly address a terabyte of memory with faster data access and higher system performance. It also supports SMP Linux, full Level 1 cache coherency and up to 8 MB of Level 2 cache.

To minimize system-level latency and increase overall system performance, the HS3x processors all support close coupled memories and direct mapping of peripherals, providing single-cycle access to other IP and memory blocks on the SoC. Native ARM® AMBA® AXI™ and AHB™ standard interfaces are configurable for 32-bit or 64-bit transactions to optimize throughput.

The ARC HS Family is supported by a robust ecosystem of software and hardware development tools, including the MetaWare Development Kit, a complete solution for developing, debugging, and optimizing embedded software on ARC processors, the MQX real-time operating system (RTOS) and a portfolio of third-party tools, operating systems and middleware from leading industry vendors through the ARC Access Program.

Key features

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

- Single-, dual- or quad-core configurations

- 64-bit loads and stores

- 64-bit multiply, multiply-accumulate

- Radix-4 hardware divider

- Optional IEEE 754-compliant floating point unit - single or double precision

- Selectable ECC protection for all memories in the processor

- Low-latency port for fast access to peripherals or memory

- Up to 240 interrupts, with up to 16 configurable preemption levels

- Native ARM® AMBA® AXI™, AHB™ interfaces

- JTAG and Compact JTAG (cJTAG) debug interface

- Optional real-time trace

- MMU with 40-bit physical address space (HS38, separately licensable for HS36)

- 4KB to 64KB instruction and data cache (HS36 and HS38 only)

- Dual- and quad-core version with support for SMP Linux with L1 coherency (HS36 and HS38)

- Up to 8MB L2 cache (HS38, separately licensable for HS36)

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Arithmetic Units IP core

ML-KEM explained: Quantum-safe Key Exchange for secure embedded Hardware

Accelerating RTL Design with Agentic AI: A Multi-Agent LLM-Driven Approach

LTE Single Carrier DFT: Faster Circuits with Reduced FPGA LUT/Register Usage

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Computing dons new suits as required

Frequently asked questions about Arithmetic Unit IP cores

What is The FastMath Pack is a math processing accelerator for the ARC HS family?

The FastMath Pack is a math processing accelerator for the ARC HS family is a Arithmetic Units IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Arithmetic Units?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Arithmetic Units IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.