SAE J1850 Verification IP

SAE_J1850 Verification IP provides an smart way to verify the SAE_J1850 component of a SOC or a ASIC.The SmartDV's SAE_J1850 Veri…

Overview

SAE_J1850 Verification IP provides an smart way to verify the SAE_J1850 component of a SOC or a ASIC.The SmartDV's SAE_J1850 Verification IP is fully compliant with standard SAE_J1850. The SAE_J1850 Verification IP can be readily customized and optimized for a wide range of specific system applications.

SAE J1850 Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SAE J1850 Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports open architecture approach.

- Supports the concept of Carrier Sense Multiple Access(CSMA) with nondestructive contention resolution.

- Supports single-level bus topology.

- Supports two types of data rate

- Data rate 10.4 Kbps

- Data rate 41.6 Kbps

- Supports the bit-by-bit arbitration.

- Supports the frame priority.

- Supports frame filtering.

- Supports two types of addressing

- Physical addressing

- Functional addressing

- Supports various type of header format

- Single byte header

- One byte form of consolidated header

- Three byte form of consolidated header

- Supports maximum number of length upto 12 bytes.

- Supports maximum number of nodes upto 32 nodes.

- Supports various types of In-Frame-Response(IFR)

- type 0-none

- type 1-single byte from a single responder

- type 2-single byte from multiple responder

- type 3-multiple bytes from single responder

- Supports CRC error injection and detection.

- Supports various kinds of errors generation and detection on SAE_J1850

- Invalid frame/message length

- Out-of-range

- Invalid bit detection

- Supports two types of bit encoding

- Pulse Width Modulation(PWM)

- Variable Pulse Width Modulation(VPM)

- Supports fault tolerance.

- Supports various types of indiviual nodes

- Unpowered nodes

- Sleeping node

- Awake/Operational node

- Supports constrained randomization of protocol attributes.

- Supports error injection in all the layers of SAE_J1850.

- Supports SAE_J2178,SAE_J2012 SAE_J1979,SAE_J2190.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Built in coverage analysis.

- SAE_J1850 Verification IP comes with complete testsuite to test every feature of SAE_J1850 specification.

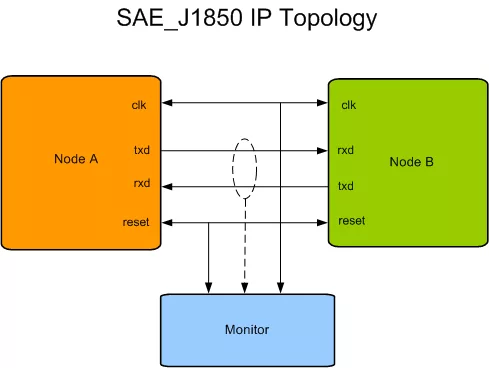

Block Diagram

Benefits

- Rich set of configuration parameters to control the functionality

- Faster testbench development and more complete verification of SAE_J1850 designs.

- Easy to use command interface simplifies testbench control and configuration of transmitter and receiver.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SAE_J1850 testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is SAE J1850 Verification IP?

SAE J1850 Verification IP is a CAN / CAN-FD / CAN-XL IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.