CAN Verification IP

The CAN Verification IP provides an effective & efficient way to verify the CAN components of an IP or SoC.

Overview

The CAN Verification IP provides an effective & efficient way to verify the CAN components of an IP or SoC. The CAN VIP is fully compliant with CAN Specification version 2.0, CAN FD (Bosch and ISO-11898-1), and CAN XL (11898-1 2022). The VIP is lightweight with easy plug-and-play components so that there is no hit on the design

Key features

- Adherent to CAN 2.0 Part A & B Specification, CAN FD (BOSCH and ISO-11898-1), and CAN XL 11898-1 2022 with ISO/DIS 16845 (Conformance test plan).

- Supports test cases as per standard.

- INTERNATIONAL STANDARD ISO/DIS 16845.

- Supports all types of frames.

- Standard and Extended Data frames

- Standard and Extended Remote frames

- Error frames

- Overload frames

- FD Base Format Frame

- FD Extended Format Frame

- Supports Time Triggered CAN specs as defined ISO 11898Part 4.

- Supports CAN with flexible data rates (FD).

- Supports CAN with CAN XL.

- Callbacks in node transmitter, receiver, and monitor for userprocessing of data.

- Complete CAN Tx/Rx functionality.

- Tracks TEC/REC error counter and fault states.

- Supports Full Duplex of operations.

- Supports constraints Randomization.

- Remote frame support.

- Automatic transmission after reception of remotetransmission request (RTR).

- Automatic receive after transmission of an RTR.

- Supports all types of error insertion and detection.

- Bit errors

- Stuff errors

- CRC errors

- Form errors

- Acknowledgment errors

- Supports Glitch insertion and detection.

- Functional coverage for complete CAN features.

- Re-transmission of corrupted messages.

- Monitors detect and notify the testbench of significantevents such as transactions, warnings, timing and protocolviolations.

- Status counters for various events on the bus.

- CAN Verification IP come with a complete test suite to testevery feature of CAN specification and Conformance testplan ISO/DIS 16845.

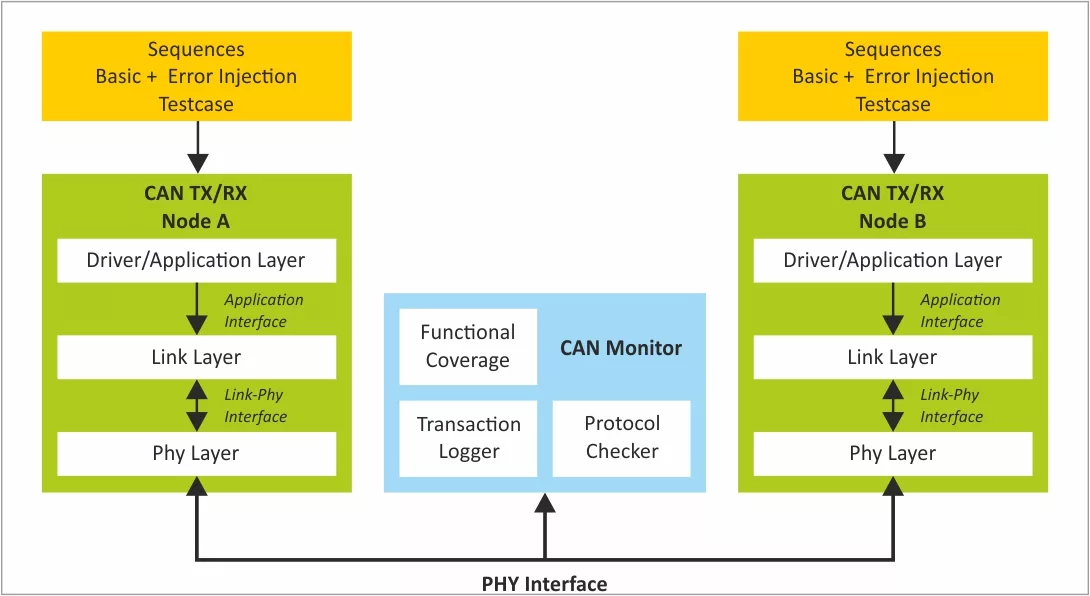

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology toensure the highest levels of quality.

- Availability of various Regression Test Suites.

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverpoints with connectivity examples for all thecomponents.

- Consistency of interface, installation,operation, and documentation across all ourVIPs.

- Provide complete solutions and easyintegration in IP and SoC environments.

What’s Included?

- CAN Tx/Rx/BFM/Agent

- CAN Monitor

- CAN Scoreboard

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Notes

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is CAN Verification IP?

CAN Verification IP is a CAN / CAN-FD / CAN-XL IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.