PLIC Verification IP

The Platform Level Interrupt Controller Verification IP provides an effective & efficient way to verify the components interfacin…

Overview

The Platform Level Interrupt Controller Verification IP provides an effective & efficient way to verify the components interfacing with RISC-V Core. It is fully compliant with standard RISC-V Privilege Spec by SiFive, Inc. This VIP internally supports other controller configurations like, APIC, CLIC and CLINT.

This is a lightweight VIP with an easy plug-and-play interface so that there is no hit on the design cycle time

Key features

- Compliant to RISC-V Privilege Spec,provided by SiFive, Inc.

- Supports all types of interrupt controller configurations

- Can also be independently configured to work as a custom Core Local Interrupt Controller

- Supports additional bus protocols ( AHB, APB, AXI etc ) for runtime programming and easy integration in an IP/SoC environment.

- Supports all the PLIC specific registers

- Interrupt Priority Registers

- Interrupt Pending Bits Registers

- Interrupt Enable Registers

- Priority Thresholds Registers

- Interrupt Claim Registers

- Interrupt Completion Registers

- Supports all the primary features of CLIC

- Reverse compatibility with CLINT

- CLIC Direct Mode

- CLIC Vector Mode

- CLIC Interrupts, Priorities & Preemptions

- Additional support for user defined configurations and specifications as needed

- Supports user specific tasks for data loading and reading for on the fly debugging

- Detailed transaction logs for data comparison and debugging

- Supports additional analysis port for custom scoreboard implementation

- Bus assertions for all possible scenarios

- Provides detailed statistics for each transaction.

- Provides a comprehensive user API (callbacks) in all BFMs.

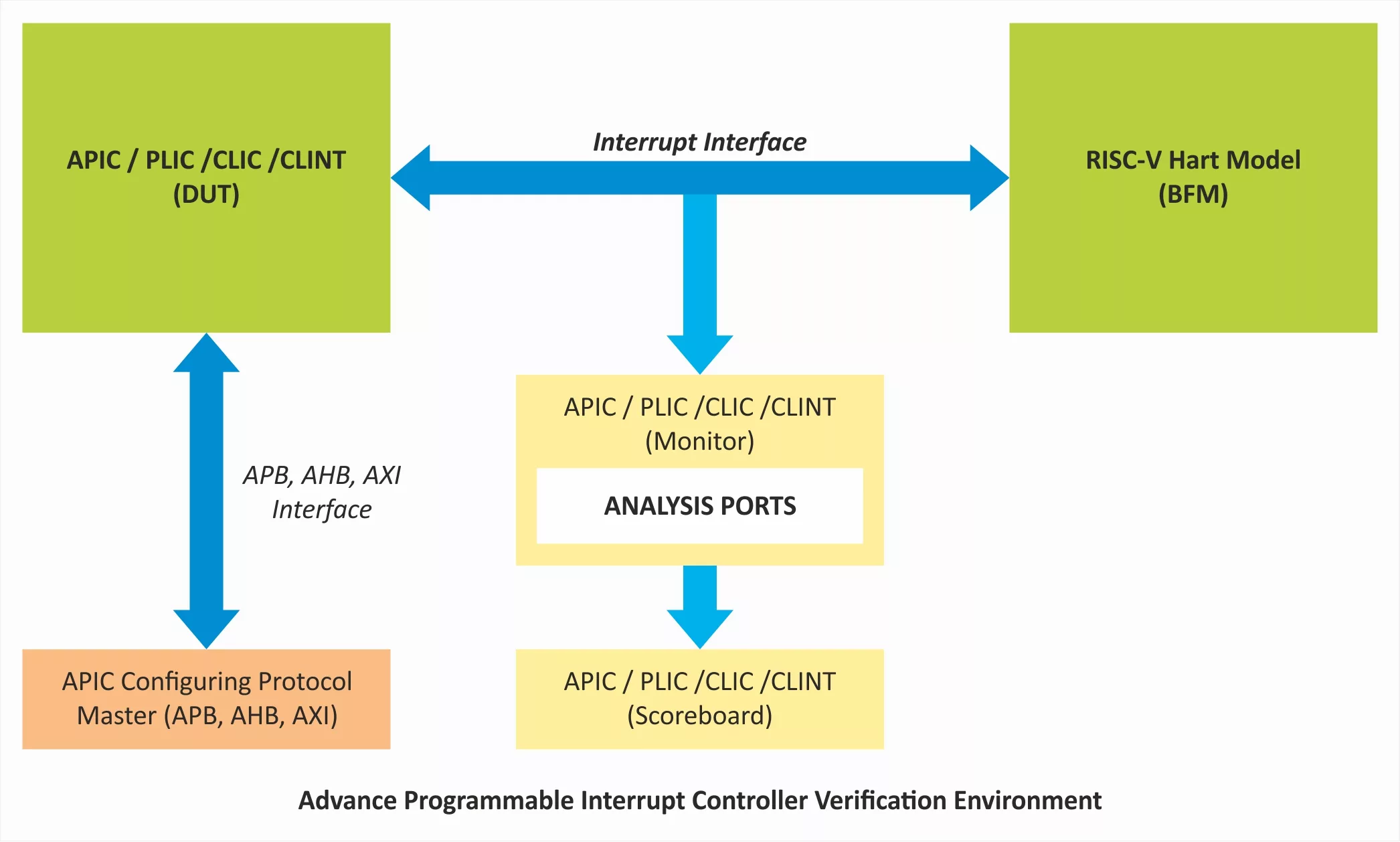

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- Availability of various Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

What’s Included?

- APIC Agent

- RISC-V Hart Model Agent

- APIC Configuring Protocol Master ( APB, AHB etc )

- APIC Bus Monitor, assertion module and Scoreboard

- Test Environment and Test Suite:

- Basic and directed protocol tests

- Random Tests.

- Assertion and cover-point Tests

- Integration guide, User Manual, FAQ, and Release Notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about Interrupt Controller IP core

Easy migration from Arm to RISC-V: an L110 case study

Migrating the CPU IP Development from MIPS to RISC-V Instruction Set Architecture

A formal-based approach for efficient RISC-V processor verification

A closer look at Arm A-profile support for non-maskable interrupts

SOC Stability in a Small Package

Frequently asked questions about interrupt controller IP cores

What is PLIC Verification IP?

PLIC Verification IP is a Interrupt Controller IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this Interrupt Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Interrupt Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.