Master and Slave SPI Bus Controller

The Serial Peripheral Interface (SPI) allows high-speed synchronous serial data transfer between microprocessors / microcontrolle…

Overview

The Serial Peripheral Interface (SPI) allows high-speed synchronous serial data transfer between microprocessors / microcontrollers and peripheral devices. The SPI-MS core can operate either as a Master or a Slave SPI bus device.

When operating in master mode, the core generates the serial data clock (SCK) and selects the slave device, which will be accessed. The SPI-MS core master is able to generate single-byte or multi-byte frames. The internal data path of the core is configurable between 8,16 or 32-bit width. When using a wider that 8-bit data-path, the core is able to generate partial word transfers, by generating frames with less bytes than the data path width. In this manner the core can transmit a data stream with length that is not a multiple of the data-path width.

When operating in slave mode, another master device on the bus generates the Serial Data Clock and activates the Slave Select input of the core to establish communication. The slave is able to split the received data in partial words, in the case that a smaller than the data-path width frame is received. The slave incorporates mechanisms to reject input noise from the SPI bus, achieving a reliable data reception. Transmitted data are also accurately synchronized with the Serial Clock of the SPI bus.

Key features

- Run-time programmable Master or slave mode operation.

- Bit rates generated in Master mode: ÷2, ÷4, ÷6, ÷8, ÷10, ÷12, ...÷512 of the system clock.

- Bit rates supported in Slave mode: fSCK ≤ fSYSCLK ÷4

- Support for 1,2,4 or unlimitted bytes multi-byte frame data transfers, run-time programmable.

- Support for partial word transfer in 2, 4 or unlimited multi-byte frame modes.

- 8 Slave Select lines.

- 8 Chip Select lines.

- Configurable RX and TX FIFOs.

- Little or Big Endian byte mapping in multi-byte frames.

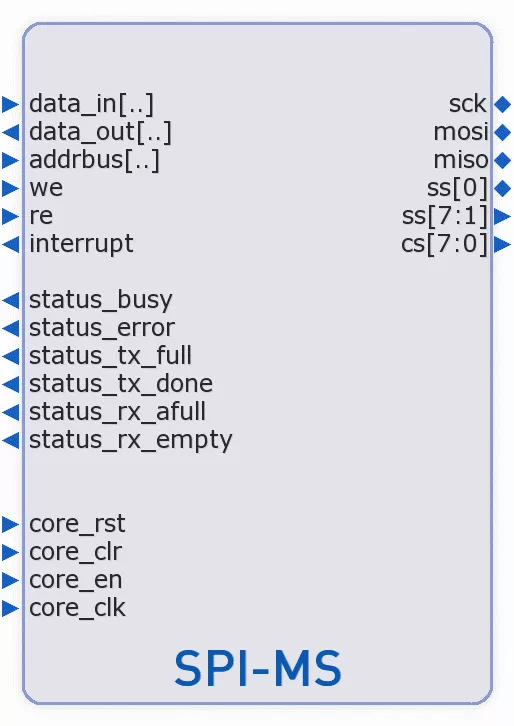

Block Diagram

Applications

- Interfacing to sensors, ADC/DAC, memories, flash cards and other peripherals using the SPI protocol

What’s Included?

- Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

- Self-checking testbench environment sources, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is Master and Slave SPI Bus Controller?

Master and Slave SPI Bus Controller is a SPI / QSPI XSPI IP core from Alma Technologies listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.