Magillem Registers System Integration Automation

Cost-effective and scalable, Magillem Registers offers a memory map view of IPs and systems based on the IP-XACT standard.

Overview

Cost-effective and scalable, Magillem Registers offers a memory map view of IPs and

systems based on the IP-XACT standard. The Registers approach targets the traditional need

to manage registers for system-on-chip solutions efficiently. It addresses today’s challenges

of HW/SW integration in complex SoCs by supporting many advanced features like the

integration of configurable large-scale IP register descriptions from different sources and

formats.

Magillem Registers improves productivity with the ability to reduce errors and misalignments

thanks to a synchronized database and comprehensive consistency checks. A single source

of truth environment ensures the synchronization between HW, SW, and documentation

and, therefore, a high-quality generated design.

Creation, editing, and review may be driven through Tcl or Python scripts and an intuitive

yet powerful register editor GUI. All reduce manual errors and cycle time to completion with

seamless integration in existing flows thanks to customizable importer/exporter and register

property definitions.

Key features

- Single database: Import and capture memory map information into a single database (IP-XACT)

- Graphical edition: IP memory map capture & management GUI, system memory map capture & management GUI, system level schematic configurability, GUI with linting cross-checking editor

- Parameterization: including configurable and conditional properties, custom-specific access types, and register modes

- SystemRDL compiler: full support of version 1.0, limited support for version 2.0

- Robust flow automation API libraries: Generator execution in CLI, TCL, and Python console, interactive shell with automatic completion, dynamic syntax checking, and inline documentation within a user-friendly environment, flexible generators customization through native Object Oriented API

- Comprehensive checkers: Integrated Design Rule Checks for syntax and semantic errors detection with on-the-fly markers and contextual resolution help, custom checks support, configurable checkers severity, checkers reports in several formats, checkers waivers

- Standard formats generation: Verilog Register Banks (AMBA, OCP, Avalon), UVM Register package (with coverage model), HW/SW Documentation (docx and HTML Format), C-code HW Access Functions (HAL layer 1, layer 2), C-code HW Verification Functions (HAL layer 3), ARM® CMSIS-SVD (1.0, 1.1, 1.2, 1.3)

- Custom templates: Advanced generation capability with support for custom template-based generators

- Merge/Flatten IP memory: Enable easy update/manipulation/creation of new global memory map for a sub-system or SoC

- Tool integration: Tight link with Magillem Connectivity to validate the system address map when both tools are combined

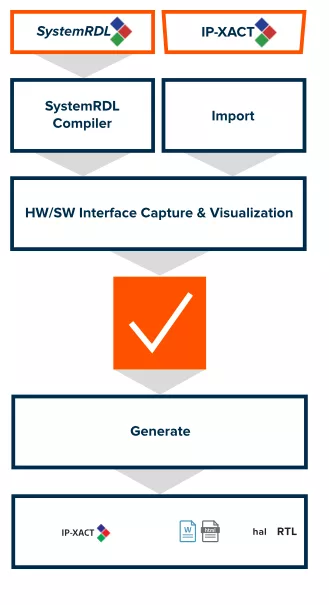

Block Diagram

Benefits

- Quick & easy adoption: Intuitive yet powerful and extensible register editor GUI cuts learning curve and eases adoption

- A single source of truth for the hardware/software interface: Generate consistent data with HW, SW and documentation all in sync to ensure accuracy and cross-team consistency

- Scalable and expansive solution: Up to hundred thousands registers

- Used for large-scale SOC memory map

- Seamless integration in existing flows: Define and customize importer/exporter/register property definitions for seamless integration

- Quality assurance: Catch errors as you enter the memory map information before running any simulation ensuring higher quality designs thanks to the built-in checkers

- Automated & efficient flow: Automatic generation of multiple and customizable output formats

- Reduce tedious and error-prone tasks shortening the overall process

- Boost Productivity: Reduce effort and rework, accelerating the schedule to signoff sw interface

- Tight link with HW interface definitions and platform connectivity

- Generate correct and aligned system map definitions for SW development.

Applications

- Management of large-scale SoC designs across all market segments.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about System Controller IP core

Low Power Asynchronous Processor With Cordic Co-Processor

Automation in IP based SoC development: Case study of a media processor subsystem

DDR2 Signal Integrity

Extreme partitioning

Reconfiguring Design -> Reconfiguring for broadband access

Frequently asked questions about system controller IP cores

What is Magillem Registers System Integration Automation?

Magillem Registers System Integration Automation is a System Controller IP core from Arteris listed on Semi IP Hub.

How should engineers evaluate this System Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this System Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.