Magillem Connectivity System Integration Automation

Magillem Connectivity is the centerpiece of a , intuitive, single source of truth design environment.

Overview

Magillem Connectivity is the centerpiece of a powerful, intuitive, single source of truth design

environment. It delivers advanced functionalities to address today’s challenges of complex SoC assembly with aggressive time-to-market constraints.

IPs packaged according to the widely supported IP-XACT standard can be instantiated, configured, and connected to build up SoC designs. Creation, editing, and review may be driven through Tcl, Python, or Java for a scripted integration, and a rich graphical user interface (GUI). RTL netlists can be generated at any time in addition to other collateral data, such as makefile scripts for an extensive range of EDA tools and connectivity reports bringing clear visibility to integration status.

Magillem Connectivity allows continuous integration with a robust, automated SoC build process that can adapt to meet changing needs within a project, ensuring error-free connectivity and drastically reducing cycle time to completion. It enables consistency and interoperability between the design flow steps with a proven correct-by-construction methodology, ensuring a high system quality.

Key features

- Project management: Design navigation and data aggregation

- HDL import: Automatic import of structural RTL into a valid IP-XACT design with the support of SystemVerilog, Verilog, and VHDL languages

- IP Packaging: Aggregate component information from different sources in a structured and standard-based format for several design tasks and teams (automatic mapping of bus interfaces, specification of the views with complete fileSet for various skills)

- SoC assembly: Powerful rule-based connectivity, bus interface detection, bus/signal split/tie/open, hierarchical connection, glue logic insertion, feedthrough

- Parameters configuration: Hierarchical propagation or overriding

- Hierarchy manipulations: Move, merge, and flatten a physical/virtual hierarchy for RTL restructuring/partitioning

- Platform derivatives: With the incremental design, automatic update, and design diff and merge capability

- Design diff and merge: Comprehensive Diff GUI showing concurrent conflicts/changes on the same IP-XACT platform, Accept/Reject any change, conflict resolution wizard (choice selection, instance renaming...), cn-the-fly checks to verify the validity of choices/conflict resolution

- IP update: Comprehensive Diff GUI, user mapping rules definition to apply during IP Update, automatic tie connection generation on new ports, automated correct-by-construction IP-XACT platform update at any level of the hierarchy, component instance view update, support instance updates for Interface/port/parameter renaming/resizing/deletion/merging

- Graphical edition: System graphical front-end editor, IP browser / IP-XACT editor, checkbox interface to connect IP (bus, signal, split, tie), drag and drop IP into the design, parameters view (all/filtered), dynamic hierarchy view, virtual hierarchy management

- Robust flow automation API libraries: Generator execution in CLI, TCL, and Python console, interactive shell with automatic completion, dynamic syntax checking, and inline documentation within a user-friendly environment

- Comprehensive checkers: Integrated Design Rule Checks for syntax and semantic errors detection with on-the-fly markers and contextual resolution help, custom checks support, configurable checkers severity, checkers reports in several formats, checkers waivers

- Advanced generation capability: RTL Netlist generation in SystemVerilog, Verilog, and VHDL, fine-tuning thanks to the preferences, configurable header, component stubbing, deep netlisting

- Automation of CAD script generation: Automatic generation of makefile scripts for an extensive range of EDA tools, support of customization

- Tool integration: Tight link with Magillem Registers to validate the system address map when both tools are combined

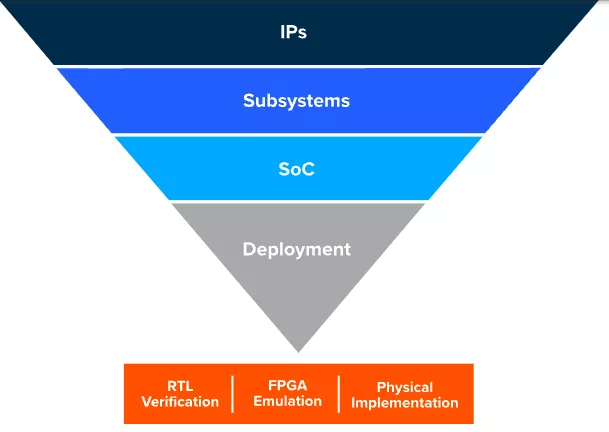

Block Diagram

Benefits

- True IP Reuse Methodology: IPs and subsystems with vendor-independent IP packaging (IP-XACT based) for reuse across design and design flows

- Shorten and streamline the IP integration process: Accelerate connectivity through automation

- Reduce iteration cycle time for integration of new IP versions, at any stage of the assembly

- Continuous Integration with a robust SOC build process: The solution is repeatable and scalable, allowing it to quickly react and adapt safely to meet changing design needs within a project or in the future

- Single Source of truth environment for system design: Empower efficient collaborative work between the design teams

- Enable interoperability between the steps of a complex design flow

- Correct-by-construction designs: Catch errors as you enter the design information before running any simulation thanks to the built-in checkers that ensure higher-quality designs

- Boost Productivity: Automation reduces the effort and rework, ensures repeatability and eliminates human errors for higher quality design and shorter time to market

- Leverage Technical Expertise: Reduce tedious and time-consuming tasks to focus on core business.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about System Controller IP core

Low Power Asynchronous Processor With Cordic Co-Processor

Automation in IP based SoC development: Case study of a media processor subsystem

DDR2 Signal Integrity

Extreme partitioning

Reconfiguring Design -> Reconfiguring for broadband access

Frequently asked questions about system controller IP cores

What is Magillem Connectivity System Integration Automation?

Magillem Connectivity System Integration Automation is a System Controller IP core from Arteris listed on Semi IP Hub.

How should engineers evaluate this System Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this System Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.