LVDS IO handling data rate up to 50Mbps with maximum loading 60pF

KA16UGLVDS01ST001 is a LVDS IO handling data rate up to 50Mbps with a maximum loading of 60pF.

Overview

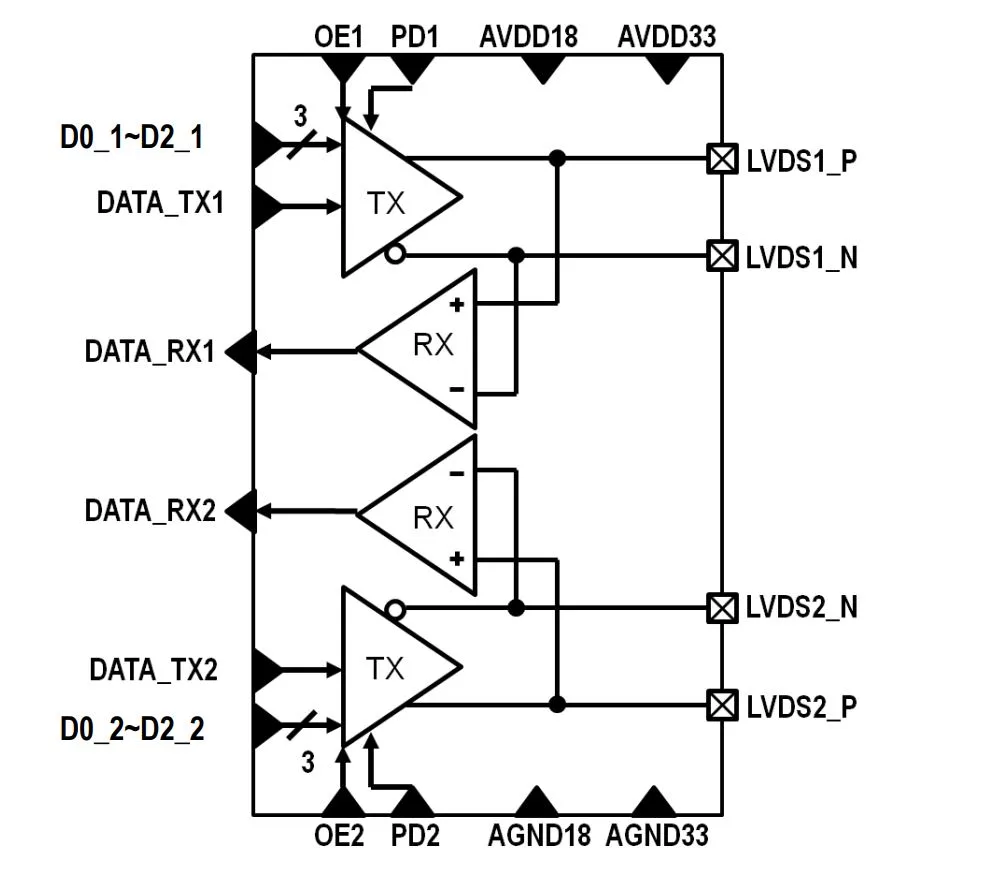

KA16UGLVDS01ST001 is a LVDS IO handling data rate up to 50Mbps with a maximum loading of 60pF. The differential voltage swing can be programmable from 0.35V to 1V. The output enable control function can be activated to decide the IO as input/output function. This IP also includes the IO PAD.

Key features

- Process: Silterra 0.16um CMOS 1P5M Process

- Supply Voltage Range: AVDD33 = 3.3v +/-10%, AVDD18 = 1.8v +/-10%

- Ambient Temperature: 0°C~80°C

- Compatible with BLVDS_25 of Spartan-3A FPGA

- Bi-direction (half-duplex)

- External Termination Resistor: RT = 120Ω

- Maximum Running Data Rate 50 Mbps with Maximum Loading 60pF

- <3-bit> Programmable Output Differential Voltage from 0.35V to 1V

- ESD: 2kV HBM and 200V MM

Block Diagram

Benefits

- The differential voltage swing can be programmable from 0.35V to 1V.

Applications

- Consumer

- Industrial Electronic

What’s Included?

- Compatible with BLVDS_25 of Spartan-3A FPGA

Specifications

Identity

Provider

Learn more about High-Speed IP core

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

Driving the Future of High-Speed Computing with PCIe 7.0 Innovation

High-Speed Test IO: Addressing High-Performance Data Transmission And Testing Needs For HPC & AI

eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

Frequently asked questions about High-Speed I/O Pad IP

What is LVDS IO handling data rate up to 50Mbps with maximum loading 60pF?

LVDS IO handling data rate up to 50Mbps with maximum loading 60pF is a High-Speed IP core from Key ASIC listed on Semi IP Hub.

How should engineers evaluate this High-Speed?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this High-Speed IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.