3.125 Gbps DDR CML receiver

065TSMC_CML_01 core logic interface includes complementary output signal pins (OUTp, OUTn) for data transmission and enable pin E…

Overview

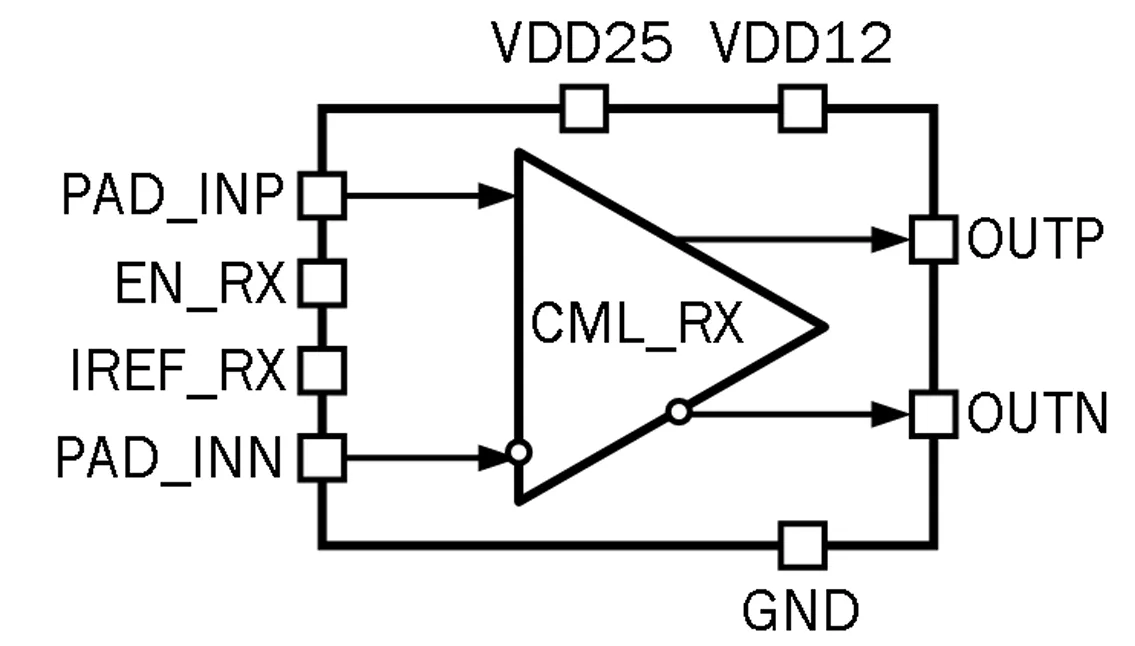

065TSMC_CML_01 core logic interface includes complementary output signal pins (OUTp, OUTn) for data transmission and enable pin EN_RX. PAD_INP and PAD_INN are differential input pins that should be connected to bonding pads. Buffer includes two 50-Ohm on-chip termination resistors, connected to supply voltage node. So the interface supports both AC and DC-coupled connections. IREF_RX is a reference current input.

Key features

- TSMC CMOS 0.065 um

- 1.2 V digital power supply

- 2.5 V CMOS input logic signals

- 1.2 V CMOS input logic signals

- 3.125 Gbps (DDR MODE) switching rates

- Temperature range: -40 °C to + 125 °C

- Optimized for pad-limited layout design

- Portable to other technologies (upon request)

Block Diagram

Applications

- Point-to-point data transmission

- Multidrop buses

- Clock distribution

- Backplane receiver

- Backplane data transmission

- Cable data transmission

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 65nm | GP | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about High-Speed IP core

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

Driving the Future of High-Speed Computing with PCIe 7.0 Innovation

High-Speed Test IO: Addressing High-Performance Data Transmission And Testing Needs For HPC & AI

eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

Frequently asked questions about High-Speed I/O Pad IP

What is 3.125 Gbps DDR CML receiver?

3.125 Gbps DDR CML receiver is a High-Speed IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this High-Speed?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this High-Speed IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.