Key Value Store/Exact Match Search Engine

The Ultra-Low-Latency (ULL) Exact Match Search Engine (EMSE) IP is latency-optimized Key-Value Store (KVS) system for Accelerated…

Overview

The Ultra-Low-Latency (ULL) Exact Match Search Engine (EMSE) IP is latency-optimized Key-Value Store (KVS) system for Accelerated Finance applications. Algo-Logic leverages FPGA Accelerations to deliver extreme look-up and IOP performance. EMSE core has the unique ability to maintain constant lookup time through an advanced table balancing algorithm input instead of a variable lookup delays common with trees and/or hash probing algorithms.

EMSE can be used either as a stand-alone FPGA IP using the hardware command interface or with an API so that data can be shared between software and logic on FPGA.

Key features

- Supports following commands in logic and software

- Insert {Key, Value}

- Value = Search {Key}

- Modify {Key, Value}

- Delete {Key}

- Parameterizable field and table sizes

- Key sizes between 80 to 640 bits

- Value sizes in increments of 8 bits

- Number of entries

- Support for larger on-chip tables

- Large tables can be stored using UltraRAM in Xilinx UltraScale+ device family

- Sharing data between logic and software

- Hardware interface enables issuing commands from FPGA logic

- C++ software API enables issuing commands from software

- Core tracks usage statistics

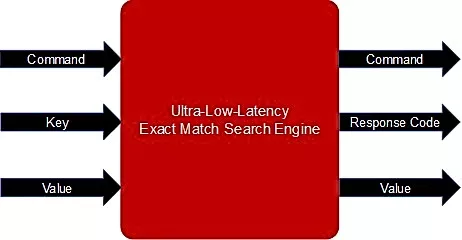

Block Diagram

Applications

- High Frequency Trading

- Tick-To-Trade systems

- Pre-Trade Risk Check systems

- Position and Exposure tracking

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Arithmetic Units IP core

ML-KEM explained: Quantum-safe Key Exchange for secure embedded Hardware

Accelerating RTL Design with Agentic AI: A Multi-Agent LLM-Driven Approach

LTE Single Carrier DFT: Faster Circuits with Reduced FPGA LUT/Register Usage

FPGA Implementation of DLX Microprocessor With WISHBONE SoC Bus

Computing dons new suits as required

Frequently asked questions about Arithmetic Unit IP cores

What is Key Value Store/Exact Match Search Engine?

Key Value Store/Exact Match Search Engine is a Arithmetic Units IP core from Algo-Logic Systems listed on Semi IP Hub.

How should engineers evaluate this Arithmetic Units?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Arithmetic Units IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.