GDDR3 Synthesizable Transactor

GDDR3 Synthesizable Transactor provides a smart way to verify the GDDR3 component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

GDDR3 Synthesizable Transactor provides a smart way to verify the GDDR3 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's GDDR3 Synthesizable Transactor is fully compliant with standard GDDR3 Specification and provides the following features.

Key features

- Supports 100% of GDDR3 protocol standard

- Supports all the GDDR3 commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports all mode registers programming

- Supports 8 bank operation

- Supports nominal and dynamic on-die termination (ODT) for data,strobe and mask signals

- Checks for following:

- Check-points include power on, initialization and power off rules

- State based rules, active command rules

- Read/write command rules etc

- All timing violations

- Supports bidirectional differential data strobe

- Supports programmable burst length:

- 4

- 8

- Supports programmable sequential/interleave burst mode

- Supports programmable CAS read latency

- Supports programmable CAS write latency

- Supports selectable BL4 or BL8 on-the-fly (OTF)

- Supports self refresh mode

- Supports automatic self refresh(ASR)

- Supports write leveling

- Supports multipurpose register

- Supports write data mask function

- Supports output driver calibration

- Supports on-die termination (ODT)

- Notifies the test bench of significant events such as transactions, warnings, timing and protocol violations

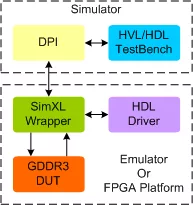

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the GDDR3 testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about GDDR IP core

SPAD: Specialized Prefill and Decode Hardware for Disaggregated LLM Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Designing the AI Factories: Unlocking Innovation with Intelligent IP

Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

The Growing Importance of AI Inference and the Implications for Memory Technology

Frequently asked questions about GDDR IP

What is GDDR3 Synthesizable Transactor?

GDDR3 Synthesizable Transactor is a GDDR IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this GDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.