Overview

All electronic systems that use CMOS digital circuits generate EM noise and currents (overlap current) as an undesired byproduct of their function. These overlap current impulses are too high in frequency for conventional regulators to supply directly, thus on-chip bypass capacitors are utilized in conjunction with system voltage regulators to supply these locally needed high frequency currents.

Adding on-chip supply bypass capacitors provide a local high frequency current reservoir for local logic, reducing supply EM noise by bypassing the digitally generated, high frequency noise currents to system ground. This capacitor bypassing action, however, shunts the high frequency EM surges and noise currents away from the supply line ultimately causing a “throw away” DC power drain (i.e. DC recharging of the bypass capacitors due to the losses and overlap currents in the system) supplied by system power sources, batteries, and capacitors.

Power draw due to these digitally derived noise currents and losses can be greater than 50% of the total device and system power consumption. They are especially significant in battery operated systems and portable devices, such as smart phones, portable computing devices, laptops and iPads, medical devices, ultra-low power systems powered by low capacity energy harvesting devices, and the like. This form of digital power drain tends to increase system size weight and Power (SWaP) as the consuming device is utilized more heavily and application complexity increases in digitally driven systems.

To reduce the above mentioned EM power drain, the conventional design wisdom is to use digital strategies in design so as to periodically deactivate power hungry digital circuits (some form of “burst mode” processing), reduce system clock rates, minimize digital supply voltages, or “process shrink” the design to a lower gate length manufacturing process node. The strategies above can be thought of as power saving “defensive” actions, the designer striving to reduce switching circuit power drain as much as possible. Utilizing the above strategies generally requires some form of design rework on the digital circuits in order to accomplish the desired power reduction, which adds to time to market and cost. It should be noted, that no matter what “defensive” choices designers make in attempting to reduce digital EM power drain, a certain magnitude of “thrown away” current and power always remains when switching circuits are active. So long as designers use electron-based transistor devices in design, this type of energy waste will be present. This form of power drain can be thought of as a previously “forgotten” EM energy source embedded in switching systems, considered unreachable and unusable, until now.

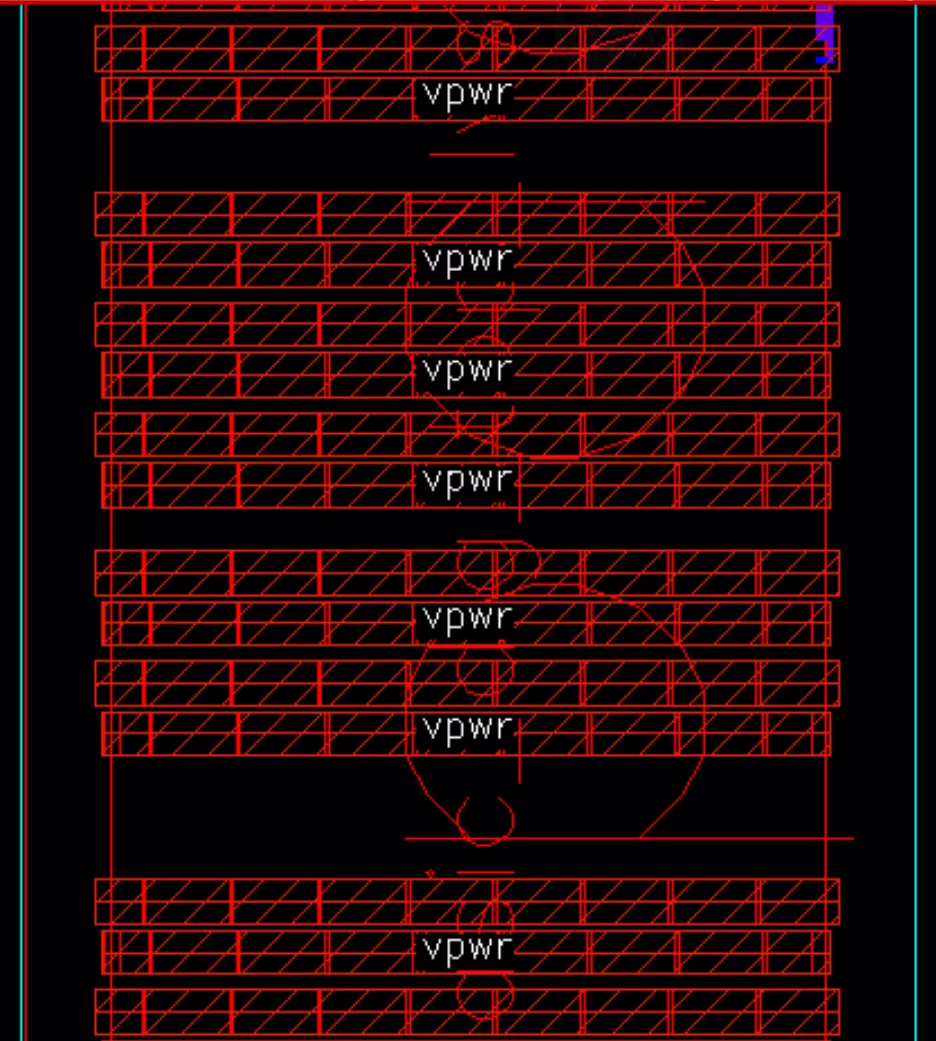

Maintaining the Fit, Form, and Function of conventional Supply Line Bondpads, the CurrentRF PowerPad Supply Line Bondpad reduces the overlap current digital power drain, tapping into this capacitor bypassed source of wasted power, recycling and reducing 20% to 40% of the total Digital Power Draw. Targeting digital “thrown away” currents, the PowerPad Supply Line Bondpad intercepts and recycles these currents back into a given IC power grid, reducing overall Digital Power Draw. The implementation of the CurrentRF Powerpad Supply Line Bondpad is small and inexpensive enough to be integrated into the padring of any Digital or Mixed Signal IC, and/or into existing and new IC bondpads, drawing no operational power of it’s own.

The CurrentRF Powerpad is currently available on TSMC and XFAB process nodes, and customizable for any modern foundry process.

Learn more about Power Management Controller IP core

This article shows several ways to implement a power management controller using the new PMBus Revision 1.3 specification, and addresses several new considerations with architecting a system using this new specification.

Rivos is pleased to announce the successful secure provisioning of the integrated OpenTitan open source Root of Trust (RoT) in its SoC. This was done during the chip production process using the ZeroRISC provisioning appliance and platform.

Seven Steps to Create a Formal IP Specification

The USB 3.1 spec supports data rates up to 10 Gbits/second but poses new hurdles in link-layer design for chip designers, says an expert in the IP group at Synopsys.

The latest PCIe 6.x specification brings groundbreaking advancements in power efficiency and performance optimization. In this technical demonstration, Senior Principal Application Engineer Julien Eydoux showcases two features of Rambus’ PCIe 6.x Controller: L0p mode and FLIT mode operation.

This paper details first PCIe errors, error logging and then the error handling on a typical SoC.