VESA DSC V1.2 Encoder

VESA introduced the first Display Stream Compression (DSC) standard in 2014.

Overview

VESA introduced the first Display Stream Compression (DSC) standard in 2014. The DSC 1.1 has been incorporated into the VESA Embedded DisplayPort (eDP) and MIPI® DSI embedded mobile interface standards. The latest VESA Display Compression-M (VDC-M) standard has also been adopted into the MIPI DSI standard. For mobile applications, DSC 1.1 and VDC-M mainly serve to reduce the video interface data rate, which reduces system power, prolongs battery life, and reduces interconnects to enable sleeker designs. For external display interfaces, DSC 1.2b extends resolution across existing connectors and cables, enabling 8K video and legacy support from the same connection.

Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB. It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

Features

- Compliant with the VESA DSC 1.2a and 1.2b standards

- Performs encoding

- Supports 8/10/12/14/16 bpc

- 4:4:4 RGB, 8, 10, and 12 bpc

- 4:4:4 YCbCr, 8, 10, and 12 bpc

- 4:2:2 YCbCr 8, 10, and 12 bpc

- 4:2:0 YCbCr, 8, 10, and 12 bpc

- Any mode, 14 and 16 bpc

- The encoder algorithm is optimized for hardware implementations at 1 pixel/clock (2 pixels/clock for Native 4:2:2 or 4:2:0 mode)

- Supports MMAP, BP, MPP and ICH

- High Performance Design

- 4K video at 60Hz

- 8K video at 30Hz (ASIC only)

Programmable display resolutions

Key features

- Capable of decoding up to 4K video at 30fps in FPGA and 8K video at 30fps in ASIC applications

- Low gate count and low latency implementation

- Three clock domains

- Stream and APB clocks operate the applicable interfaces

- Independent decoder clock runs the core functions

- Fully compliant with the VESA Display Stream Compression(DSC) 1.2 standard

- Uses synchronous design techniques and a technology abstraction layer for internal SRAM buffers

- Allows for migration from FPGA or FPGA prototype to ASIC with no functional changes to the core

- Completely pipelined; can be stalled as necessary to properly manage input and output rate

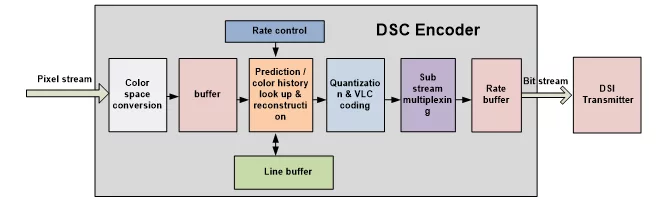

Block Diagram

Benefits

- Fully compliant to VESA standards

- Small footprint

- Code validated with HAL and 0-in-CDC

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers

What’s Included?

- Verilog HDL of the IP Core

- Synthesis scripts

- Verification environment

- User guides for design and verification

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about VESA DSC IP core

MIPI: Powering the Future of Connected Devices

VESA Video Compression on MIPI DSI-2 Enables Next-Generation Display Applications

Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

Revolutionizing Display Technology with VESA Display Stream Compression (DSC) Decoder IP

VESA Display Stream Compression (DSC) Encoder IP Core

Frequently asked questions about VESA DSC IP cores

What is VESA DSC V1.2 Encoder?

VESA DSC V1.2 Encoder is a VESA DSC IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this VESA DSC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this VESA DSC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.