Vendor:

Methods2Business

Category:

Wi-Fi

IEEE 802.11 ah WiFi HaLow

WiFi HaLow adapts the familiar WiFi standard to a frequency and connection style that is ideally suited to the Internet of Everyt…

Overview

WiFi HaLow adapts the familiar WiFi standard to a frequency and connection style that is ideally suited to the Internet of Everything.

Operating in the sub gigahertz range, this standard delivers 1 km range in point-to-point links and > 1km in 2-hop relays. By using a token-ring style of client management, a single HaLow access point can completely support up to 8191 clients, and provides adaptive bandwidth to each client based on their identified data transport needs.

The Aegis-IP 802.11 ah core is a complete digital platform implementing the MAC and Baseband layers of this protocol. The core is available in one of three major configurations: as a low power sensor node; as a full featured sensor node, and as an access point.

The Aegis 802.11 ah cores all include a bus master AXI interface to provide maximum throughput with minimal process intervention, and a processor core with additional bandwidth to host your application. When combined with a suitable radio from one of our partners, this core gives you everything you need to enable your products to join the Internet of Everything.

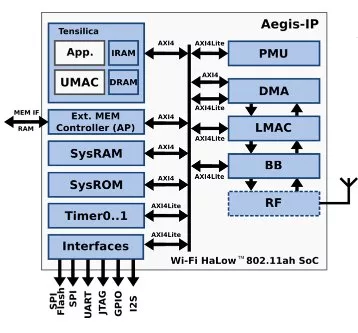

A typical customer application, depcited below, includes a suitable processor core where the Media Access Controller upper firmware (UMAC) resides, as well as the customer application.

Typical ApplicationThe Power Management Unit (PMU) wakes up and shuts down the core as an integral part of the low power operation, enabling sensor nodes to run up to three years on a single charge.

The integrated DMA engine, and the Lower Mac (LMAC) offload processing task from the processor core, further saving power.

The BaseBand (BB) provides all of the forward error correction, digital to analog conversion, data recovery and error correction features in very efficient hardware; and interfaces to the supported radio cores (RF).

The System RAM and System ROM are accessble from the AXI4 bus, as well as a set of timers and general interface engines.

Coded in System C and built with the Cadence HLS and Virtual Platform tools, user customization is readily available.

Operating in the sub gigahertz range, this standard delivers 1 km range in point-to-point links and > 1km in 2-hop relays. By using a token-ring style of client management, a single HaLow access point can completely support up to 8191 clients, and provides adaptive bandwidth to each client based on their identified data transport needs.

The Aegis-IP 802.11 ah core is a complete digital platform implementing the MAC and Baseband layers of this protocol. The core is available in one of three major configurations: as a low power sensor node; as a full featured sensor node, and as an access point.

The Aegis 802.11 ah cores all include a bus master AXI interface to provide maximum throughput with minimal process intervention, and a processor core with additional bandwidth to host your application. When combined with a suitable radio from one of our partners, this core gives you everything you need to enable your products to join the Internet of Everything.

A typical customer application, depcited below, includes a suitable processor core where the Media Access Controller upper firmware (UMAC) resides, as well as the customer application.

Typical ApplicationThe Power Management Unit (PMU) wakes up and shuts down the core as an integral part of the low power operation, enabling sensor nodes to run up to three years on a single charge.

The integrated DMA engine, and the Lower Mac (LMAC) offload processing task from the processor core, further saving power.

The BaseBand (BB) provides all of the forward error correction, digital to analog conversion, data recovery and error correction features in very efficient hardware; and interfaces to the supported radio cores (RF).

The System RAM and System ROM are accessble from the AXI4 bus, as well as a set of timers and general interface engines.

Coded in System C and built with the Cadence HLS and Virtual Platform tools, user customization is readily available.

Key features

- Functionality

- STA Infrastructure BSS

- Single stream

- Channel Bandwidth: 1MHz and 2MHz

- Frame Type: S1G_1MHz, S1G_short and detects S1G_long PPDU

- MCS: 0,1,2 and 10

- FEC: BCC

- Normal Guard Interval

- Fixed Pilot

- QoS for 1 and 4 priority queues

- MPDU Aggregation

- Block Acknowledgement

- RSNA (WPA2) Security

- Target Wake Time (TWT)

- Restricted Access Window (RAW)

- Authentication control

- Supported Processors

- Cadence® Xtensa® Fusion DSP

- ARM Cortex M0+ and other processors on request

- Interfaces

- UART/I2C/SPI/JTAG

- Radio

- External Required Components

- SPI Flash

- Performance

- Up to 2 Mbps

- Low BER

- Up to 1 km range

- Software

- MAC 802.11ah Stack

- APIs for C applications and AT commands

- Integrated TCP/IP stack

- On-chip bootloader and programming interface

- Xtensa® XOS

- CPU/DSP can be used as application processor

Block Diagram

IEEE 802.11 ah WiFi HaLow block diagram

What’s Included?

- Synthesizable Verilog RTL

- for implementation in an FPGA or ASIC (specify technology file)

- SystemC models

- for use in Aegis-IP Wi-Fi HaLow virtual platform

- MAC SW stack, API's & integrated TCP/IP stack on lightweight OS

- Reference testbench and applications

- Demonstration FPGA Board

- with the core(s) implemented in a Xilinx FGPA, with firmware loaded into the board's flash memory, and room for your application hardware and software.

- Custom Orders

- Aegis IP is ready to customize the core to add or modify functionality to meet your specific needs.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

IEEE 802.11 ah WiFi HaLow

Vendor

Methods2Business

Provider

Methods2Business

HQ:

The Netherlands

Methods2Business aims to be among the leaders in a new class of IP providers utilizing the latest EDA tools and a proven system-level design methodology to build, with minimal effort and resources, the next generation semiconductor IP products which are highly customizable, verifiable and include all the hardware/software models needed for modern system on chip designs.

Learn more about Wi-Fi IP core

Wi-Fi 7 (IEEE 802.11be) & MLO vs. Wi-Fi 6/6E (IEEE 802.11ax): What to Ask for Optimal Design Considerations

Franz Dugand, Ceva

How to achieve better IoT security in Wi-Fi modules

A look at the architecture of Wi-Fi modules and the opportunities for designers to improve IoT device and network security by using the resources available in these modules.

Designing a Wi-Fi HaLow Baseband in Less than Six Months

Protecting Wi-Fi chipsets with hardware-based security cores

CEVA's XC12 DSP Core Targets Multi-Gbit Cellular, Wi-Fi Opportunities

Frequently asked questions about Wi-Fi IP cores

What is IEEE 802.11 ah WiFi HaLow?

IEEE 802.11 ah WiFi HaLow is a Wi-Fi IP core from Methods2Business listed on Semi IP Hub.

How should engineers evaluate this Wi-Fi?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Wi-Fi IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.