CAN Synthesizable Transactor

CAN Synthesizable Transactor provides an smart way to verify the CAN component of a SOC or a ASIC in Emulator or FPGA platform.

Overview

CAN Synthesizable Transactor provides an smart way to verify the CAN component of a SOC or a ASIC in Emulator or FPGA platform. CAN 2.0 Synthesizable Transactor is an advanced solution in the market for the verification of CAN 2.0(A & B) implementations. It is adherent with CAN 2.0 VIP (plus addendum specification) and it supports all frame types such as Data, Remote, Overload and Error frames. The CAN VIP monitor acts as powerful protocol-checker, fully compliant with CAN 2.0 specification.

CAN 2.0 Synthesizable Transactor includes an extensive test suite covering most of the possible scenarios and CAN conformance norms. It can perform all protocol tests as testbench Bosch and moreover it allows an easy generation of very high number of patterns and a set of specified patterns to stress the DUT.

Key features

- Adherent to CAN 2.0 Part A & B Specification and ISO/DIS 16845(Conformance test plan)

- Supports Time Triggered CAN specs as define ISO 11898 Part 4

- Supports CAN with flexible data rate

- Suports complete CAN Tx/Rx functionality

- Supports Full Duplex of operations

- Supports test cases as per standard

- INTERNATIONAL STANDARD ISO/DIS 16845

- Supports all the four frame types

- Data frames

- Remote frames

- Error frames

- Overload frames

- supports remote frame support

- Automatic transmission after reception of remote transmission request (RTR)

- Automatic receive after transmission of an RTR

- Supports all the five types of error insertion and detection

- Bit errors

- Stuff errors

- CRC errors

- Form errors

- Acknowledgement errors

- Tracks TEC/REC error counter and fault state

- Supports glitch insertion and detection

- Supports re-transmission of corrupted messages

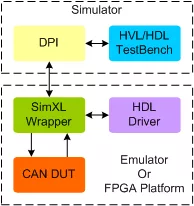

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the CAN testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CAN / CAN-FD / CAN-XL IP core

Fraunhofer/CAST CAN XL IP Core Succeeds in First Multi-Vendor Plugfest

Frequently asked questions about CAN / CAN FD / CAN XL IP cores

What is CAN Synthesizable Transactor?

CAN Synthesizable Transactor is a CAN / CAN-FD / CAN-XL IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CAN / CAN-FD / CAN-XL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CAN / CAN-FD / CAN-XL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.