Binary-PSK Demodulator

The BPSK_DEMOD IP Core is a 16-bit resolution Binary-PSK demodulator based on a multiply-filter-divide architecture.

Overview

The BPSK_DEMOD IP Core is a 16-bit resolution Binary-PSK demodulator based on a multiply-filter-divide architecture. The design is robust and flexible and allows easy connectivity to an external ADC.

As the carrier recovery circuit is open-loop, there is no feedback path or loop-filter to configure. This results in an extremely simple circuit with a very fast carrier acquisition time. The only requirement is that the user must set the desired symbol period and a suitable threshold level for the bit decisions at the symbol decoder. The other design parameters including carrier frequency, symbol rate and sampling frequency should be specified by the user before delivery of the IP Core.

The input data samples are 16-bit signed (2's complement) values that are synchronous with the system/sample clock. Input values are sampled on the rising edge of clk when en is high.

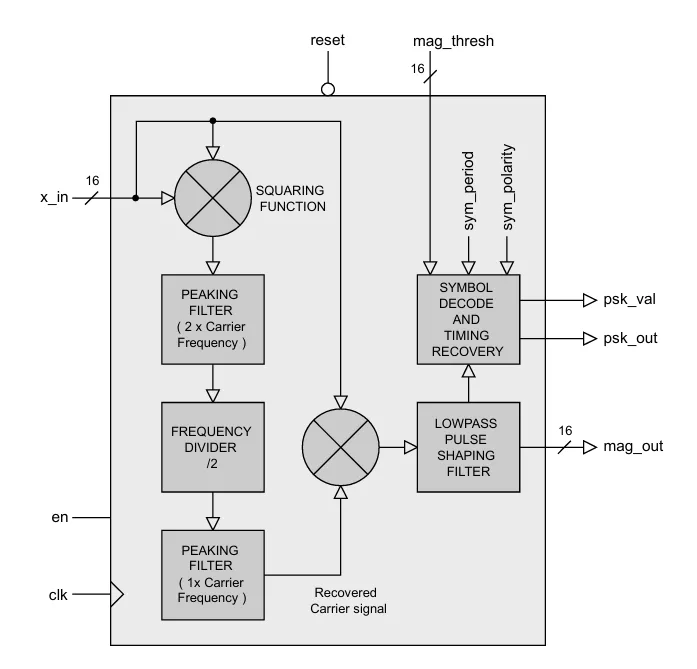

Figure 1 shows the basic architecture in more detail. The input signal is first squared in order to generate a harmonic at twice the carrier frequency and zero phase-shift. This squared signal is then filtered and divided in frequency to recover the original carrier. A second filter is employed to isolate a clean carrier signal which is used to demodulate the original input signal. The demodulated input signal then goes through a low-pass pulse-shaping filter before a bit-decision is made at the symbol decoder.

The demodulated BPSK bit-stream appears at the output psk_out. Bits are valid on the rising edge of clk when both psk_val and en are high.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human readable VHDL (or Verilog) source code

- 16-bit signed input data samples

- Automatic carrier acquisition with no complex setup required

- User specified carrier frequency, symbol rate and sample rate

- Practical symbol rates of up to 10 Mbits/s

- Typical FPGA sample rates of up to 200 MHz

Block Diagram

Applications

- Software radio

- Short to medium-range telemetry

- IF, SRD and ISM band devices

- Robust, low bandwidth radio applications for small FPGA devices

- Low-cost radio links over a few 100 meters using either wireless or cable - e.g. coax or twisted pair

- Applications where fast carrier acquisition is essential - e.g. where data packets are transmitted in short discrete bursts

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Modulation Demodulation IP core

Three Major Inflection Points for Sourcing Bluetooth Intellectual Property

Part 2: Opening the 5G Radio Interface

An Integrated, Tunable RF Filter: an Enabler for Reconfigurable Front-Ends

Design considerations for integrated CMOS receivers

Silicon IP for Programmable Baseband Processing

Frequently asked questions about Modulation and Demodulation IP cores

What is Binary-PSK Demodulator?

Binary-PSK Demodulator is a Modulation Demodulation IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Modulation Demodulation?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Modulation Demodulation IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.