ATA-7 (UDMA 133) Host controller

A ATA-7 compliant host controller core to interface to ATA devices like hard-disks, CD and DVD drives.

Overview

A ATA-7 compliant host controller core to interface to ATA devices like hard-disks, CD and DVD drives. This core is targeted for SOC implementations in ASIC and FPGA.

Key features

- PIO modes 0-4

- Multi-word DMA modes 0-2

- Ultra DMA modes 0-6

- Programmable timings for PIO and DMA modes

- Support for Ultra DMA pause and termination

- Standard slave Wishbone interface to microprocessor/microcontroller

- Interrupt generator for IRQ driven software driver implementation

- Transparent (pass through) access from processor interface to device task registers

- DMA engine and master Wishbone interface for data transfer

- Small register FIFOs for transmit and receive data

- 66MHz clock for UDMA133 (mode 6) operation

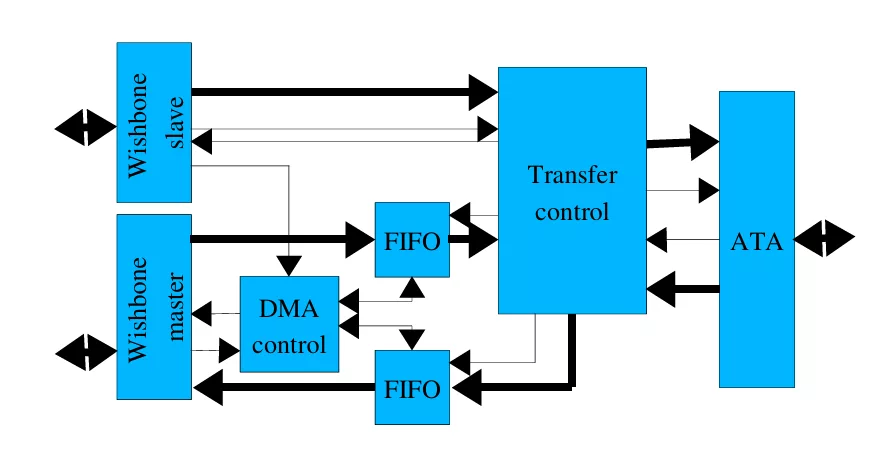

Block Diagram

Benefits

- Flexible

- Compact

- Cost-effective

- Many Shipping Products

What’s Included?

- Verilog Source Code

- Test Bench

- Sample Syntheis scripts

- Dcumentation

- Refernce Resign

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SATA Controller IP core

Verification of USB 3.0 Device IP Core in Multi-Layer SystemC Verification Environment

Designing Around an Encrypted Netlist: Is The Pain Worth the Gain?

STBus complex interconnect design and verification for a HDTV SoC

Interface IP: Winners, Losers in 2013

The IP Paradox: Sales are growing despite Semi Consolidation

Frequently asked questions about SATA Controller IP

What is ATA-7 (UDMA 133) Host controller?

ATA-7 (UDMA 133) Host controller is a SATA Controller IP core from ASICS World Services, LTD. listed on Semi IP Hub.

How should engineers evaluate this SATA Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SATA Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.