AHB Channel with Decoder and Data Mux IP Core

The AHB Channel provides the necessary infrastructure to connect as many as 7 AHB Slaves (numbered 1-7) to an AHB bus Master.

Overview

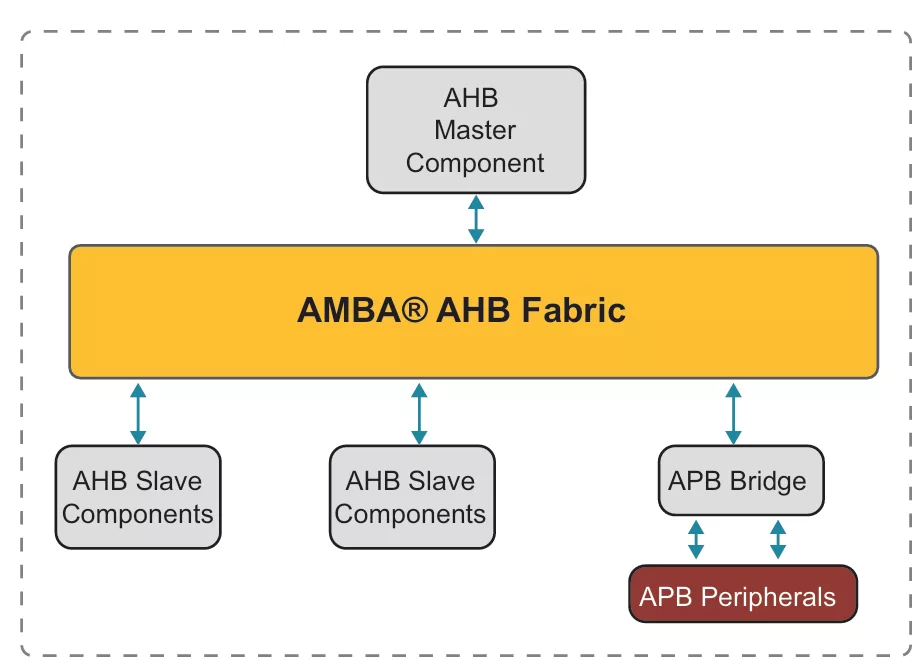

The AHB Channel provides the necessary infrastructure to connect as many as 7 AHB Slaves (numbered 1-7) to an AHB bus Master. The AHB Channel performs a combinational decode on the incoming AHB address to produce the block selects for the various AHB Slaves. The address decoder contained in the AHB Channel has one area of memory reserved for a configurable remap application.

Typically, the AHB Channel is connected as in the following description. Each of the AHB Channel’s 7 Mirrored Slave Ports is connected to an AHB Slave module (e.g. External Bus Interface, Memory Controller, AHB-to-APB Bridge.) On the Master side, the AHB Channel’s Mirrored Master Port is connected either to an AHB Arbiter (in an AHB system with multiple bus Masters) or directly to an AHB Master such as a micro-processor (in an AHB system with a single bus Master.)

Key features

- AMBA® 2.0 Compatible

- Simple AHB Infrastructure for up to 7 AHB Slaves

- Multiple Masters can be easily accommodated using AHB Arbiter

- Includes Address Decoding

- Includes Read Data Muxing

- Remap to assist boot loading and debug

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Bus Fabric IP core

Arteris loses its brain, continues walking

Secure Mobile Payments - Protecting display data in TrustZone-enabled SoCs with the Evatronix PANTA Family of Display Processors

SoC low-power verification requires a full-chip solution

The best of both worlds: Optimizing OCP slave memory behavior

Changing SoC Design Methodologies to Automate IP Integration and Reuse

Frequently asked questions about On-Chip Bus IP cores

What is AHB Channel with Decoder and Data Mux IP Core?

AHB Channel with Decoder and Data Mux IP Core is a Bus Fabric IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Bus Fabric?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Bus Fabric IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.