512-bit Vector DSP IP, Dual Core with Functional Safety

The ASIL B and C compliant ARC® VPXxFS DSP IP is a family of VLIW/SIMD processors enabling automotive system-on-chip (SoC) design…

Overview

The ASIL B and C compliant ARC® VPXxFS DSP IP is a family of VLIW/SIMD processors enabling automotive system-on-chip (SoC) designers to accelerate advanced driver assistance systems (ADAS), RADAR and LiDAR sensor processing application development and ISO26262 certification for systems using digital signal processing.

The VPXxFS Family supports multiple vector lengths and core configurations:

128-bit vector word – VPX2FS (single core), VPX2FSx2 (dual core)

256-bit vector word – VPX3FS (single core), VPX3FSx2 (dual core)

12-bit vector word – VPX5FS (single core), VPX5FSx2 (dual core), VPX5FSx4 (quad core)

The VPXxFS Family comes with integrated hardware safety features such as ECC protection for memories and interfaces, safety monitors and lockstep mechanisms that achieve the most stringent levels of ISO 26262 functional safety compliance.

To speed application software development, the VPXxFS Family is supported by the vendor’s ARC MetaWare tools, which provide a comprehensive and vector-length agnostic software programming environment that enables code portability among all members of the VPXxFS family. The tool suite includes a safety-certified optimizing C/C++ vector compiler, debugger, instruction set simulator, as well as vector-based DSP, machine learning inference and linear algebra libraries.

Key features

- Integrated hardware safety features with minimal area and power impact for full ASIL compliance (ASIL D systematic, up to ASIL C random)

- Four-way VLIW architecture combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector lengths

- 8, 16, and 32-bit integer SIMD engines

- IEEE 754-compliant vector floating point unit option offers single-precision or half precision operations and advanced math functions

- Dual vector floating point SIMD pipes

- Hardware acceleration for linear and non-linear math functions

- Single- and multicore-configured offerings

- ARC MetaWare tools including a safety certified auto-vectorizing C/C++ compiler, debugger, simulator, vector DSP and vector linear algebra libraries, and neural network SDK

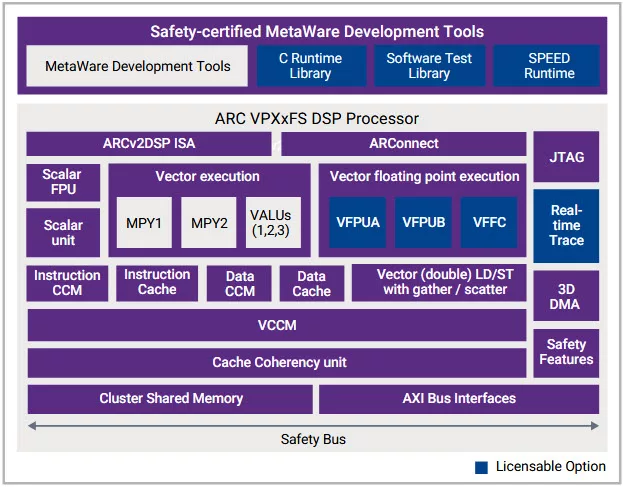

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DSP Core IP core

Wireless 5G BTS Need Super DSP core... CEVA XC-12

CEVA-X1 DSP Core Targets Cellular IoT Opportunities

Oxford Digital Offers Small Audio DSP Core With Graphical Programming

icyflex: an ultra-low power DSP core for portable applications

FPGA configures DSP core in imaging app

Frequently asked questions about DSP Core IP cores

What is 512-bit Vector DSP IP, Dual Core with Functional Safety?

512-bit Vector DSP IP, Dual Core with Functional Safety is a DSP Core IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this DSP Core?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DSP Core IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.