3D LUT Intel® FPGA IP

As a part of the Video and Vision Processing (VVP) Suite Intel® FPGA IP, the 3D look-up table (LUT) Intel® FPGA IP provides an ef…

Overview

As a part of the Video and Vision Processing (VVP) Suite Intel® FPGA IP, the 3D look-up table (LUT) Intel® FPGA IP provides an efficient solution for video color space and dynamic range conversions, chroma keying, and the creation of artistic effects.

3D LUT Intel® FPGA IP Offers Efficient Video Solutions By:

- Enabling various artistic and cinematic effects.

- Supporting SDR to HDR, HDR to HDR, and HDR to SDR conversions and PQ/HLG and log-transfer functions.

- Supporting cube sizes of 9³, 17³, 33³, and 65³.

- Applying tetrahedral interpolation.

- Utilizing industry-standard interfaces to ease the integration into your FPGA design.

- Minimizing resource utilization compared to competing products enables a more cost-effective solution.

Key features

- Support up to 4 pixels in parallel (PIP) per clock processing.

- Low subframe latency (21 clock cycles).

- Support for 17³, 33³ and 65³ LUTs.

- Support 3 and 4 output channels from the LUT (Alpha /key channel).

- High-quality tetrahedral interpolation.

- Independently set input/output pixel depth.

- Independently set LUT precision.

- Dynamic update of table values with optional double buffering to enable clean synchronous switching to a new LUT.

- Includes ‘.cube’ file format conversion utility.

- Support for 8, 10, 12, and 16-bit per color component.

- Support resolutions up to 4K at 60 fps on Intel® Cyclone® 10 FPGAs, Intel® Arria® 10 FPGAs, Intel® Stratix® 10 FPGAs, and Intel Agilex® 5 FPGA E-Series.

- Support resolutions up to 8K at 60 fps on Intel Agilex® 7 FPGAs and on Intel Agilex® 5 FPGA D-Series.

- AXI4-Stream video I/O interface.

- AXI4-Stream ↔ Avalon® streaming interface protocol converters.

- Avalon® memory-mapped CPU control and memory interfaces.

- Low resource utilization for edge applications.

- Free Intel® FPGA IP Evaluation Mode.

- Design example available.

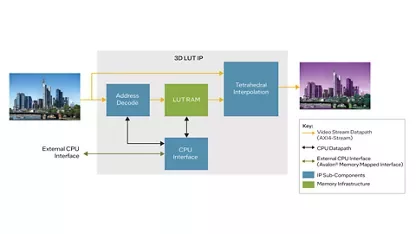

Block Diagram

Applications

- Color Space Conversions, e.g., HD Rec 709 to UHD Rec 2020

- Color Correction – Film/Video Post Production

- Chroma Keying – Virtual Studios, graphics overlays

- Color replacement – TV commercials, medical imaging

- Dynamic Range Conversions (SDR-HDR)

- Artistic effects, e.g., sepia tone, monochrome, color-space volume adjustments

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is 3D LUT Intel® FPGA IP?

3D LUT Intel® FPGA IP is a Image Conversion IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.