SDA OCT Encoder and Decoder

The Optical Communications Terminal (OCT) Standard was developed by the Space Development Agency (SDA) with the purpose of bringi…

Overview

The Optical Communications Terminal (OCT) Standard was developed by the Space Development Agency (SDA) with the purpose of bringing interoperability across freespace optical communication (FSO) systems where at least one endpoint is a space-based terminal.

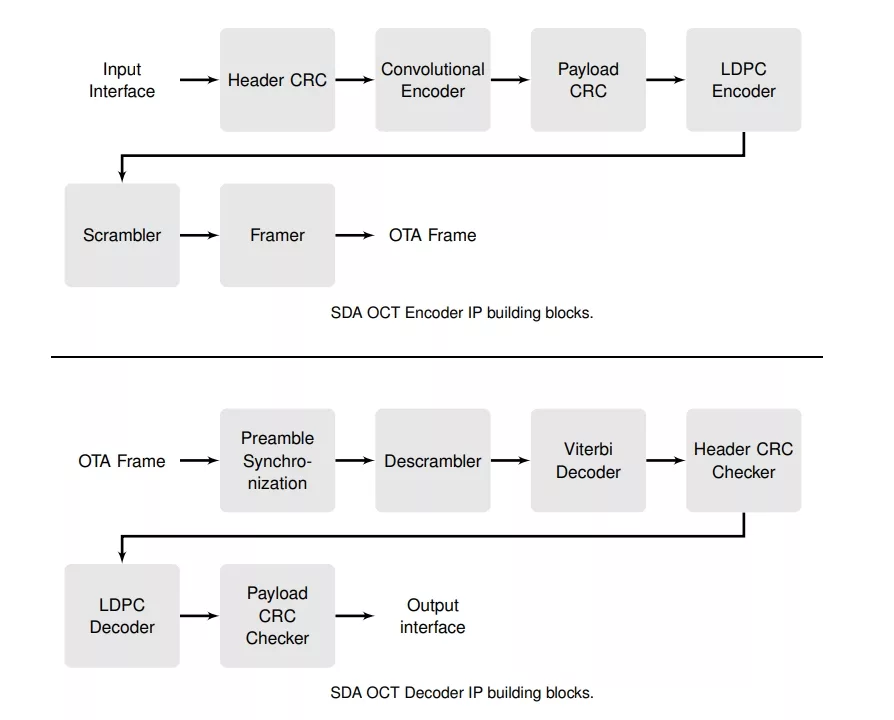

The Creonic SDA OCT Encoder handles the construction of Over-The-Air (OTA) frames as indicated in the standard, a preamble followed by a header and payload data, with both fields being protected by cyclic redundancy check (CRC) and forward error correction (FEC).

The Creonic SDA OCT Decoder performs the synchronization of the Over-The-Air (OTA) frame and then decodes the header and payload data within the frame.

Performance Figures

- Coded throughput of 2.5 Gbit/s

Key features

- Compliant with "Optical Communications Terminal (OCT) Standard Version 3.0, Document ID: SDA-9100-001-05, August 2021"

- Compliant with "Optical Communications Terminal (OCT) Standard Version 3.1.0, Document ID: SDA-9100-001-08, March 2024"

- Compliant with "Optical Communications Terminal (OCT) Standard Version 4.0.0, Document ID: SDA-9100-001-09, August 2024"

- Support for payload code rates 11/13, 22/29, 2/3, 1/2, and uncoded data

Block Diagram

Benefits

- Low-power and low-complexity design.

- AXI4-Stream data and configuration interfaces for a seamless integration.

- Collection of statistical information (frame counters, CRC error counters, synchronization loss counters, etc.)

- Configurable preamble synchronization.

- Available for AMD Xilinx FPGAs.

- Available for Intel FPGAs.

Applications

- Free-space optical communications (FSO) systems such as

- space-to-space (S2S)

- space-to-air (S2A)

- space-to-maritime (S2M)

- space-to-ground (S2G)

What’s Included?

- VHDL source code or synthesized netlist with testbench

- HDL and Bit-accurate Matlab, C or C++ simulation models

- Vivado IP Package

- Comprehensive documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is SDA OCT Encoder and Decoder?

SDA OCT Encoder and Decoder is a Image Conversion IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.