ZLIB compatible compression and decompession, with DMA and AXi interface

This is a high performance, small footprint ZLIB compatible IP Core.

Overview

This is a high performance, small footprint ZLIB compatible IP Core. It features 3 DMA engines, AXI interconnect and separate clocks for AXI interfaces and compression/decompression engines.

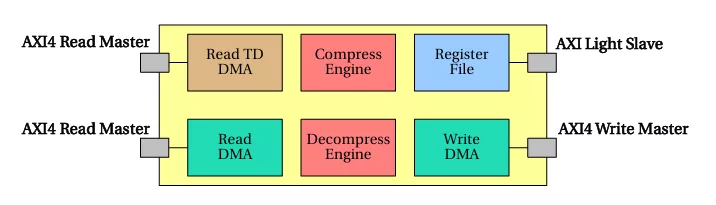

ARCHITECTURE

Separate DMA engines for Scatter/Gather descriptors and data movement, alow non stop processing of data.

Key features

- 100% ZLIB compatible

- Fixed Huffman encoding

- Subset of LZ77

- Scatter/Gather DMA engine

- Utilizes linked list of transfer descriptors

- Compression and Decompression in one IP Core

- Configurable Data Path to 32, 64 or 128 bit

- Fully AXI-4 compatible

- AXI-Light for register Interface

- Separate clocks for engines and AXI interface

Block Diagram

Benefits

- High Performance

- small footprint

Applications

- any

What’s Included?

- Verilog Source Code

- Test Bench

- Documentation

- Tech Support

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Data Compression IP core

Data compression tutorial: Part 3

Firmware Compression for Lower Energy and Faster Boot in IoT Devices

A configurable FPGA-based multi-channel high-definition Video Processing Platform

IP Core for an H.264 Decoder SoC

Digital Associative Memories Based on Hamming Distance and Scalable Multi-Chip Architecture

Frequently asked questions about Data Compression IP

What is ZLIB compatible compression and decompession, with DMA and AXi interface?

ZLIB compatible compression and decompession, with DMA and AXi interface is a Data Compression IP core from ASICS World Services, LTD. listed on Semi IP Hub.

How should engineers evaluate this Data Compression?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Data Compression IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.