Overview

The growth in wireless communication systems, cellular mobile radio and VoIP technology has created the imperative need for bandwidth efficient, high speed quality voice coding algorithms. The fundamental principle of the CVSD algorithm is the encoding of one bit per sample. For example an audio signal sampled at 32 KHz will be compressed to 32 Kbps.

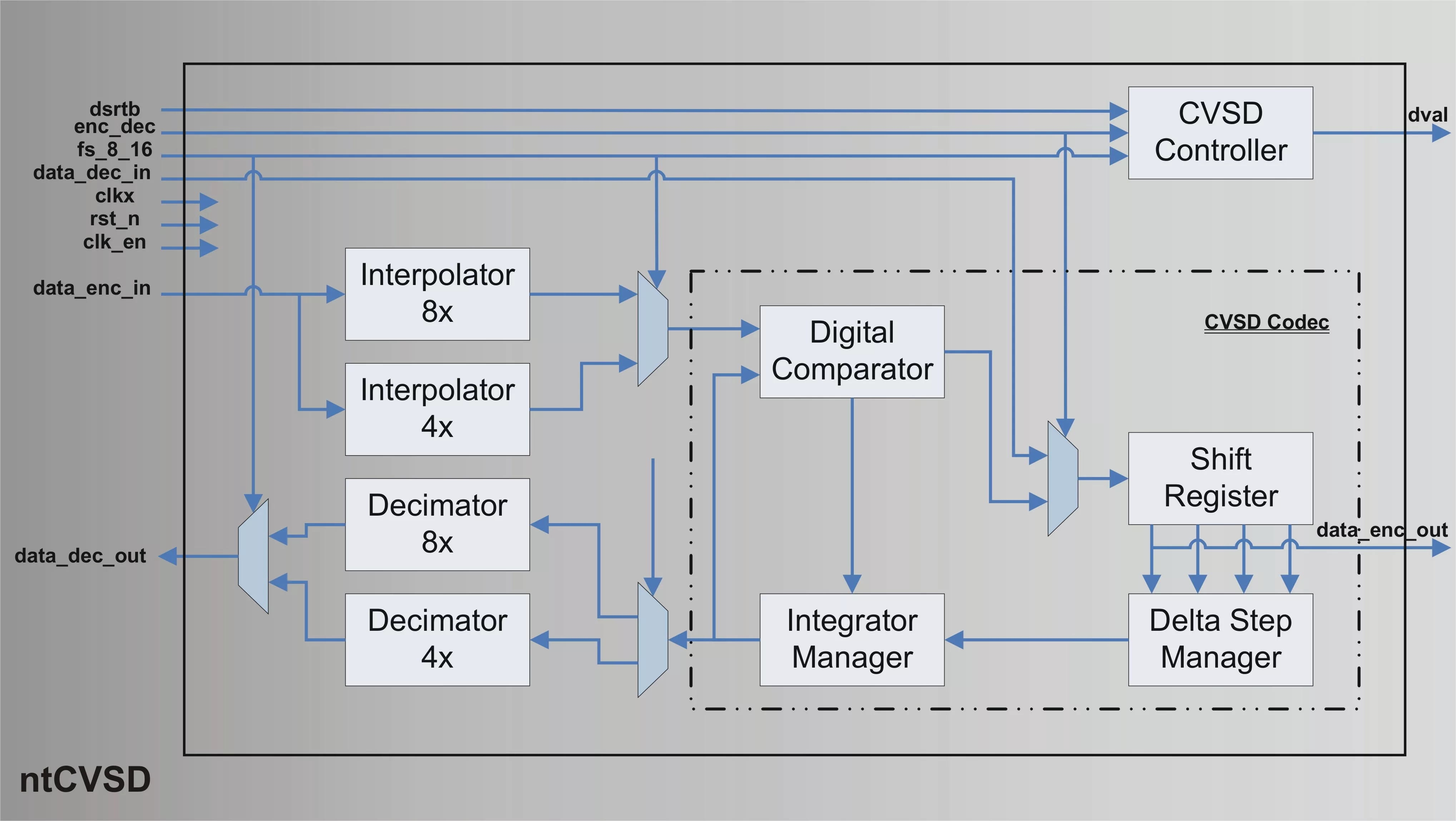

The ntCVSD codec IP core can be configured to operate either as an encoder or as a decoder functional block. In encoder mode the core accepts input data at a rate of 8 KHz/128 Kbps or 16KHz/256Kbps and are sampled when the data strobe signal is asserted high. Higher input sampling data rates can also be supported with no up-sampling provision. The sampled input data can either be initially up-sampled to 64 KHz by using an interpolation filter in order to improve speech/audio quality before entering into the actual CVSD codec unit or can be just directly fed into the CVSD codec unit with no previous pro-cessing. These samples are then driven to a digital comparator in or-der to be compared with a reference signal value. If the input sample is greater than the reference signal then a logic 1 is transmitted and a step value is added on the reference signal. If the input sample is less than the reference signal then a logic 0 is transmitted and a step val-ue is subtracted from the reference signal. The transmitted bits are also stored in an N-bit shift register. Depending on the shift register contents, a decision is made whether a slope overload has occurred and the step value is adjusted accordingly in order to keep up with the changing slope of the input waveform. Depending on both the digital comparator and the slope overload decisions, an integrator estimation is generated in order to approximate the previous input value and drive it back to the digital comparator.

In decoder mode the core accepts the compressed bit-stream and the incoming bits are sampled when the data strobe signal is asserted high. The received bit-stream is fed directly to the N-bit shift register and depending on the shift register contents, a decision is made whether a slope overload has occurred. The uncompressed signal is reconstructed through the integrator unit. The reconstructed output will be either be fed into the decimation filter to be down-sampled at the original sampling rate and then driven at the output or will be just directly driven at the output with no previous processing.

Learn more about Data Compression IP core

Data compression plays a critical role in modern computing, enabling efficient storage and faster transmission of information. Among lossless data compression algorithms, GZIP, ZSTD, LZ4, and Snappy have emerged as prominent contenders, each offering unique trade-offs in terms of compression ratio, speed, and resource utilization. This white paper evaluates these algorithms and their corresponding hardware cores, providing an in-depth comparison to help developers and system architects choose the optimal solution for their specific use case.

Part three of this three-part series explains how JPEG and MPEG compression work.

The phrase “IoT” for Internet of Things has exploded to cover a wide range of different applications and diverse devices with very different requirements. Most observers, however, would agree that low energy consumption is a key element for IoT, as many of these devices must run on batteries or harvest energy from the environment.

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

This paper presents the development of an IP core for an H.264 decoder. This state-of-the-art video compression standard contributes to reduce the huge demand for bandwidth and storage of multimedia applications. The IP is CoreConnect compliant and implements the modules with high performance constraints.

In this paper, we present a new concept and its circuit implementation for high-speed associative memories based on Hamming distance