Warping Engine IP Core

TES Warping Engine is a specialized IP core for arbitrary high-performance re-mapping of bitmaps from memory to memory.

Overview

TES Warping Engine is a specialized IP core for arbitrary high-performance re-mapping of bitmaps from memory to memory. Applications are for example pre-warping for projection on head-up displays or fisheye-correction of camera images.

The IP core adapts to different bus interfaces like AMBA APB and AHB/AXI as well as the Altera Avalon bus interface at different bus width (e.g. 32, 64, 128 bits).

Application Example: HUD warping

Projecting a rectangular image onto a curved surface yields a curved image. For a rectangular image to appear rectangular on a curved surface, it needs to be re-mapped first using the ‘inverse curvature’. The projected image is then mapped into a non-rectangular region of the output image with ‘transparent’ (i.e. normally black) pixels all around:

When the output image is projected onto the windshield, it will appear rectangular from the driver position point of view.

Application Example: Fisheye correction

Here the input image is distorted, while the output image is rectangular. Also the output image contains only pixels which exist in the input image (no ‘outside’ pixels like in the above HUD example). Still, the re-mapping is possible using an arbitrary look-up table per output pixel, which references the respective coordinates from the input image.

Key features

- Arbitrary mapping

- Based on a output->input look-up table per pixel

- Highly-efficient compression algorithm for the mapping LUT

- High-quality bilinear filtering

- 16 x 16 subpixel positions

- High performance

- Sophisticated caching mechanism proven in TES rendering engines

- Allows real-time warping of videos or rendering output

- Flexible Color Formats

- Input and output formats selectable at run-time

- Available formats fully configurable at synthesis time, e.g.:

- ARGB8888

- ARGB4444

- ARGB1555

- RGB565

- RGBA8888

- RGBA4444

- RGBA5551

- 8 bit grayscale

- etc.

- Definition of outside color

- For seamless blending with possibly transparent background

- Easy configuration via registers (less than 20 functional registers)

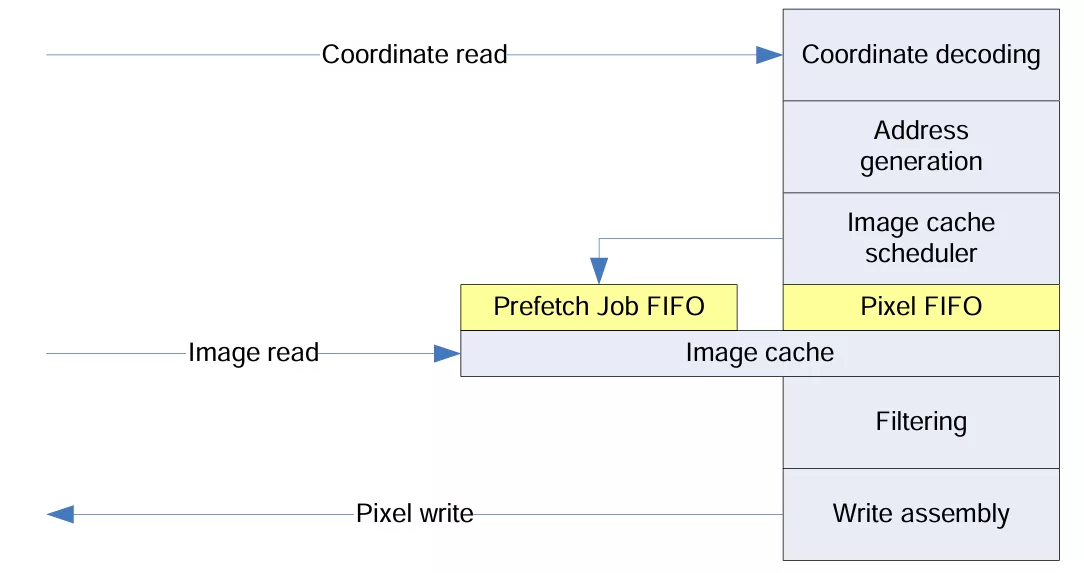

Block Diagram

Benefits

- Highly configurable Warping Engine supporting cropping as well as scaling.

- Warping Look-Up-Table with TES adaptive compession technology for optimal trade of between warping error and memory bandwidth consumption.

- Powerful tooling for generation of Warping Look-Up-Tables

- Easy SoC Integration

- Low resource consumption

Applications

- Camera fish-eye correction

- Image transformation, cropping and scaling

- Head-Up-Displays

- Projectors

What’s Included?

Software Tools

TES provides free-of-charge tools:

- GUI tool for generation of example mappings using splines to model the mapping

- Command line tool to convert a plain LUT to the compressed format

Simple to use software driver

- Only about 20 different API functions

- Separate hardware-abstraction layer allowing easy porting to other platforms (e.g. different OS, different bus interface to warping engine etc.).

- Provided as C source code

FPGA Evaluation Kit

TES offers a free-of-charge evaluation kit for Altera FPGAs with the following content:

- Altera Quartus II / QSys projects for multiple Altera/Terasic standard evaluation boards (e.g. VEEK-MT, VEEK-MT-C5SoC)

- Warping Engine as Qsys component

- Encrypted VHDL

- OpenCore Plus hardware evaluation (timeout after 1 hour)

- Nios II + Altera SoC Yocto Linux drivers as source

- Software tools to generate the compressed LUT format (see above)

- Software API documentation (HTML)

- Example software projects

- Tutorials/HowTos

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is Warping Engine IP Core?

Warping Engine IP Core is a Image Conversion IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.