Scalable Ultra-High Throughput 8/10/12-bit JPEG Encoder with Video Rate Control

The UHT-JPEG-E core is a scalable, ultra-high throughput, 8-bit Baseline and 10/12-bit Extended hardware JPEG encoder, with optio…

Overview

The UHT-JPEG-E core is a scalable, ultra-high throughput, 8-bit Baseline and 10/12-bit Extended hardware JPEG encoder, with optional video rate control functionality, designed to provide all the power needed in modern image and Ultra HD video compression applications. The scalability of this IP core enables highly cost-effective silicon implementations of applications that need to handle massive pixel rates and resolutions. The UHT-JPEG-E is available for ASIC or AMD-Xilinx, Efinix, Intel, Lattice and Microchip FPGA and SoC based designs.

This ultra-fast JPEG encoder IP core is fully compliant to the ITU T.81 specification and supports encoding of 4:4:4, 4:2:2, 4:2:0 and 4:0:0 (grayscale) images or video streams, in 8-, 10- or 12-bit per component color depth. The UHT-JPEG-E can be implemented using only on-chip memory resources, while using off-chip memory too is also natively supported. Designed with a user configurable architecture, the encoder scales to offer a sustained encoding throughput from 1 to 32 samples per clock cycle.

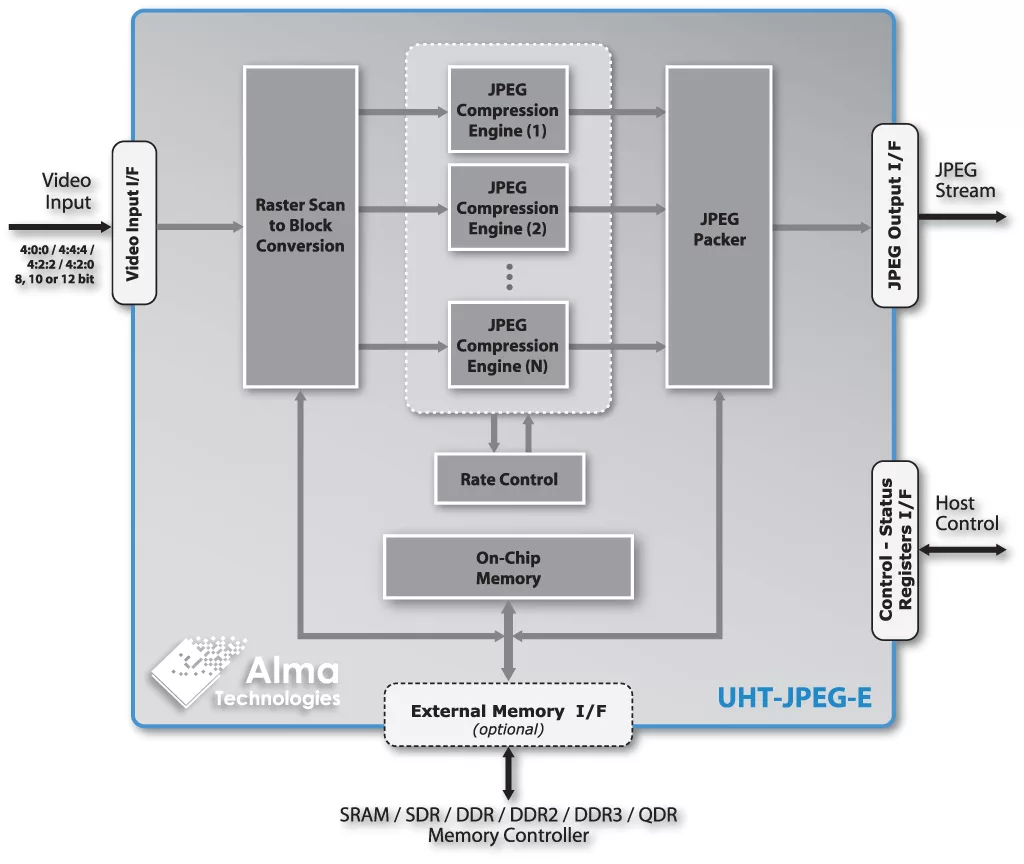

Using multiple internal processing engines, the UHT-JPEG-E offers the needed performance through its scalable parallel architecture. Each input image or video frame is split internally into chunks and each chunk is assigned to one of multiple internal compression units. This is done in a way which is totally transparent to the system utilizing the IP, abstracting all the parallelization complexity from the rest SoC components. The number of internal compression units is configurable before synthesis, adapting to the implementation technology speed, and non-critical resources are shared between the multiple compression engines.

The UHT-JPEG-E uses a single uncompressed data input interface - accepting raster scan pixels - and produces a single, ready-to-use and fully compliant JPEG stream output. The encoder employs also a constant bitrate video encoding option, making it a best fit for the bandwidth or storage constrained Motion JPEG video applications. Its operation is completely standalone, without needing any host CPU or GPU power. The output JPEG byte stream can be decoded, as is, by any standard compliant decoder.

The UHT-JPEG-E core is designed with simple, fully controllable and FIFO-like, streaming input and output interfaces. Being carefully designed and rigorously verified, the UHT-JPEG-E is a reliable, easy-to-use and integrate IP providing a best value solution for your FPGA or ASIC design.

Key features

- High-Performance, Compliant and Standalone Operation

- Ultra high throughput in low-end silicon using scalable and transparent parallel processing

- Full ITU T.81 compliance

- 4:4:4, 4:2:2, 4:2:0 and 4:0:0 (grayscale) image or video input

- 8-, 10- and 12-bit per component sample depth encoding

- Single - multiple pixels - raster scan interleaved input and single, ready-to-use, JPEG byte stream output

- Motion JPEG payload encoding

- CPU-less, complete and standalone operation

- Advanced Implementation

- Up to 32 samples per clock cycle encoding

- Algorithmic encoding latency of approximately 32 scan lines for 4:2:0 and 16 scan lines for all other sampling formats

- CQP - VBR encoding mode with programmable Quality Factor (1 to 100)

- Constant Bitrate (CBR) video encoding mode

- Programmable output frame size

- Programmable transmission buffer size

- On-the-fly video bitrate changes supported

- Configurable full on-chip or mixed on/off-chip memories implementation

- Flexible optional off-chip memory interface

- Independent of external memory type

- Tolerant to latencies

- Allows for shared memory access

- Can optionally operate on independent clock domain

- Avalon-ST and AXI4-Stream compliant streaming data I/O

- Trouble-Free Technology Map and Implementation

- Fully portable, self-contained RTL source code

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Safe CDC transfers when using more than one clock domain

- No special timing constraints required

- No false or multi-cycle paths within the same clock domain

- No CDC transfers that need to be constrained (all CDC paths can be excluded)

Block Diagram

What’s Included?

- Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

- Self-checking testbench environment sources, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is Scalable Ultra-High Throughput 8/10/12-bit JPEG Encoder with Video Rate Control?

Scalable Ultra-High Throughput 8/10/12-bit JPEG Encoder with Video Rate Control is a Image Conversion IP core from Alma Technologies listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.