Overview

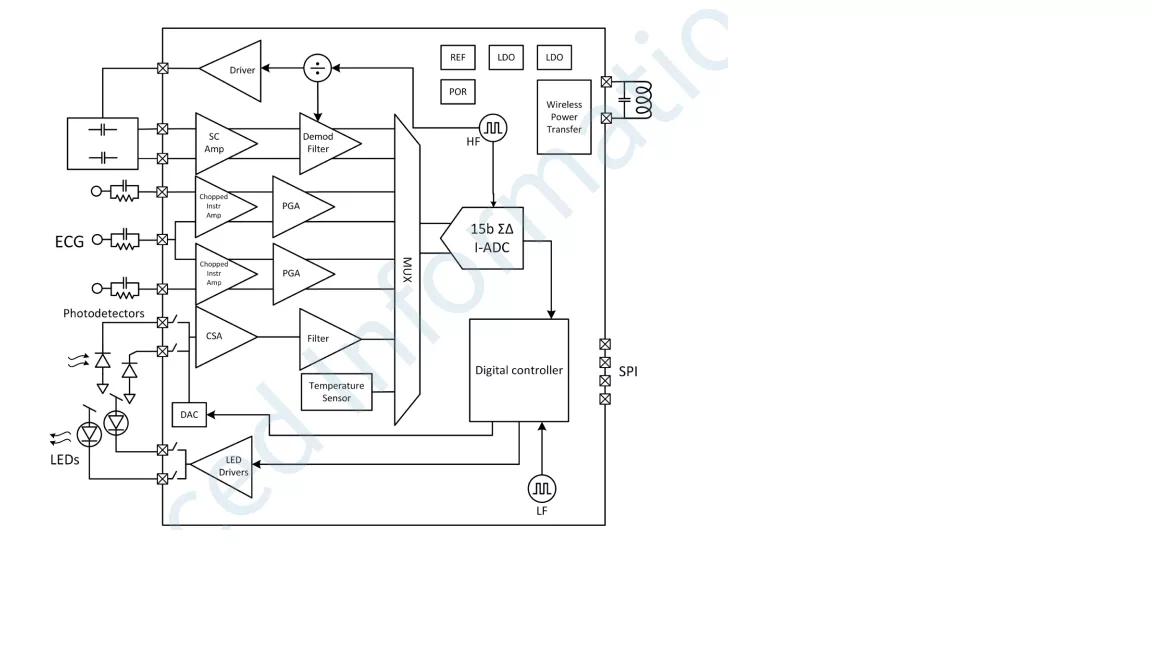

EN62020 can be interfaced with an array of ultra low-power biometric sensor front-ends for vital signs monitoring for healthcare and wearable applications. It is designed to be used alongside an edge processor or communication devices.

ENS62020 supports the accurate and reliable measurement of ECG, optical signals (PPG (HR), SpO2, Near InfraRed Spectroscopy, Fluorescent Glucose Sensing), temperature and differential capacitance

Learn more about Analog Front End IP core

Based on the system specification of a typical smart meter, this article demonstrates the importance of carefully selecting the power metering IP solution so that its specification matches the standard requirements and copes with the application challenges. This article then pinpoints thoroughly the various issues that must be taken into account for the selection of the Silicon IP and helps identify the possible trade-offs between the performance of the Mixed-signal Front-end (MFE) and that of the Power and energy Computation Engine (PCE).

In this paper we present a methodology to model and verify a mixed-signal IP using SystemVerilog in Virtuoso and NCsim. We take our 12.5Gbps transmitter (TX) design as an example to explain the method we propose. This TX is designed to operate at programmable data rates from 1.25Gbps – 12.5Gbps and to support requirements of multiple serial protocols like USB, PCIe, and SATA. Interaction between AFE and Digital is key towards proper implementation of features like Feed Forward Equalization (FFE), programmable output swing and power management states.

Like most types of circuits, there is no such thing as a "one size fits all" PLL. This article will explore the trade-offs in PLL performance and design and look for a solution to most SOC PLL needs.

As clocks speed increase and the number of clocks increases, a programmable clock generator may offer a better system and EMI design solution

Standard CMOS Ultrawideband Single-Chip Solutions

Comms rides power lines via optical AFE