USB Power Delivery 3.1 Physical Layer

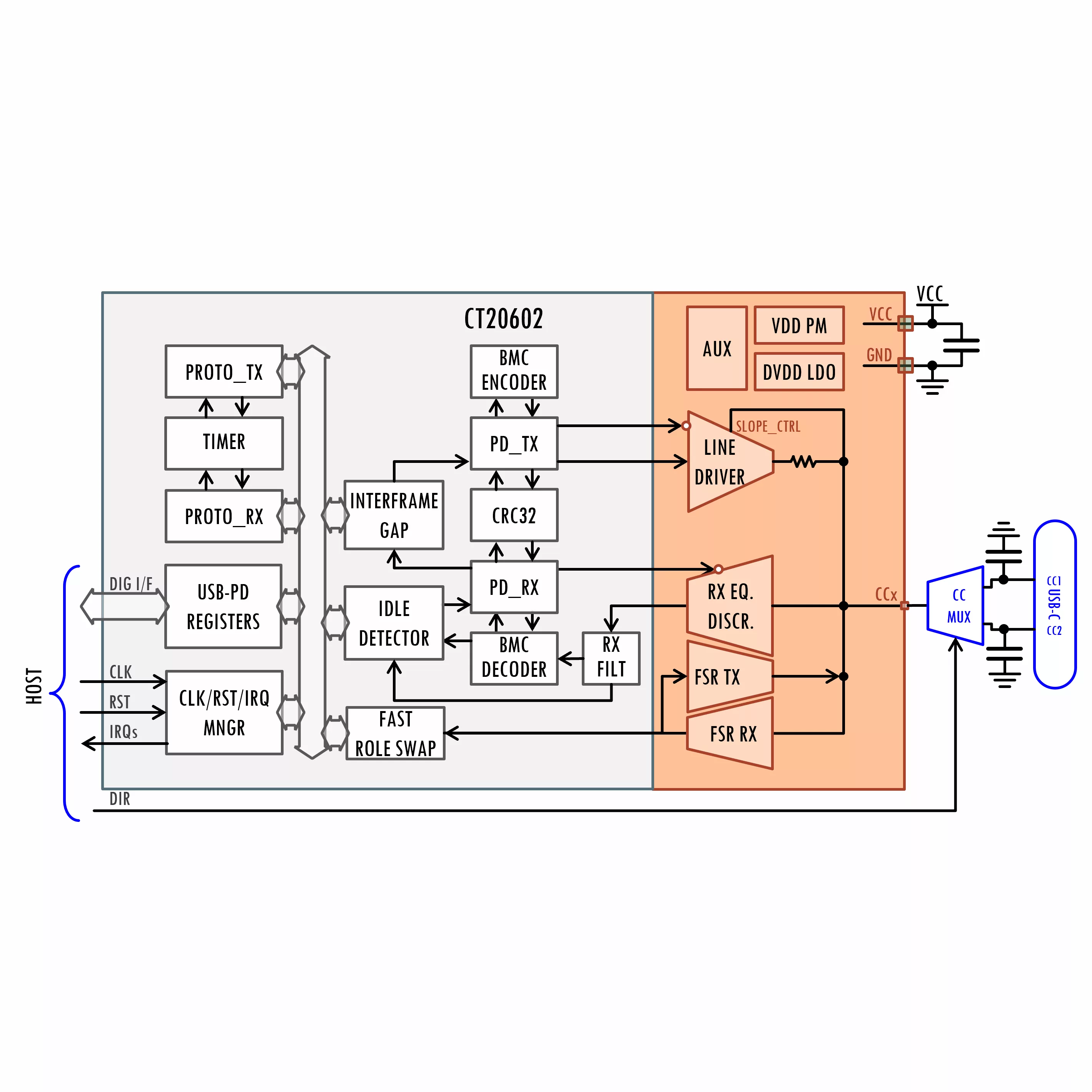

CT20602 is a USB Power Delivery 3.1 Physical Layer.

Overview

CT20602 is a complete USB Power Delivery 3.1 Physical Layer.

It also implements that part of the USB Power Delivery 3.1 Protocol Layer which is defined in the Type-C Port Controller specification, to simplify the integration with the Power Delivery Host Controller.

The Analog Front-End implements the slew-rate controlled transmitter block, the receiver block (fully compatible with the entire directives for line noise and cable DC offset and transients) and the Fast Role Swap transceiver.

The digital section of the PHY:

- Formats and sends messages,

- Formats and sends signals

- Receives and validates messages

- Receives signals

- detects incoming HardReset or CableReset signals

- Grants the inter-frame gap

- Supports SOP, SOP’ and SOP” and messages

- Supports BMC BIST modes

- Receive and Send Fast Role Swap signal

CT20602 interfaces with the Host by means of a set of standardized registers which buffers USB-PD data packets and provides commands to control operations.

Key features

- USB Power Delivery 3.1-certified

- Auto GOOD-CRC and Auto Retry

- Configurable Dual-Role, Source or Sink only

- Includes Fast-Role Swap Transceiver

- Dedicated Registers-sets and/or TCPC compliant

- Low Power

- No external components

- Voltage and current references, test infrastructures, included

Block Diagram

Applications

- USB-PD Interface

- Active Cables

Specifications

Identity

Standards & Interfaces

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB Power Delivery 3.1 Physical Layer?

USB Power Delivery 3.1 Physical Layer is a Single-Protocol PHY IP core from Canova Tech Srl listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.